目录

1 译码器简介

2 二进制译码器

2.1 2线-4线译码器

2.2 3线-8线译码器

2.3 3线-8线译码器实例74HC138

2.4 二进制译码器的应用

1 译码器简介

具有译码功能的组合逻辑电路是译码器。译码是编码的逆过程,是将输入的二进制代码转换为对应的输出信号。

译码器按照功能可以分为:变量译码器、码制译码器以及显示译码器。如下所示为译码器分类:

2 二进制译码器

二进制译码器的特点是输入n个变量,即n位代码,输出有个,即对应的n个变量的

个组合,每一种组合对应一种输入代码。

2.1 2线-4线译码器

如下图所示为2线-4线译码器的电路图:

在上面的电路中,真值表如下所示:

如下所示为图2中的使能控制端的门电路:

由上图可知,当

时,2线-4线译码器能够正常输入,在其他情况时,电路不能正常输入。

如下所示为电路中的输入缓冲器示意图

在上图中两个输入反相器是输入缓冲器,输入信号可能因传输线噪声或干扰产生毛刺,使用两个反相器作为输入缓冲器可以减少噪声和产生的毛刺。

2.2 3线-8线译码器

3线-8线译码器的逻辑框图如下所示:

3线-8线译码器可以得到:

真值表为:

用二极管和门电路组成的3线-8线译码器如下所示:

(本图为清华大学王红《数字电子技术基础》课本图片)

假设电源电压为5V,输入信号的高、低电平为3V和0V,二极管导通的压降为0.7V,当时,

、

、

为0V,取反后全部为3V,这是只有

为高电平。

2.3 3线-8线译码器实例74HC138

74HC138是一种CMOS3线-8线译码器,是将3位的二进制输入转换为8位互斥的低有效的有效输出,常用于地址译码、存储器选通和多信号分配。

通过上面的可以归纳为:。

74LS138的电路图如下所示:

74HC138的逻辑框图如下所示:

74HC128的功能表如下所示:

2.4 二进制译码器的应用

(1)地址译码

译码器的常用就是用于表示微处理的外围设备和存储单元的地址。

例如现在有一个微处理器,想要与8个设备之间进行数据交换,如下图所示:

上图中实现了对外设接口芯片的片选段的分时控制,在任何时刻,只能有一个外围设备输出。

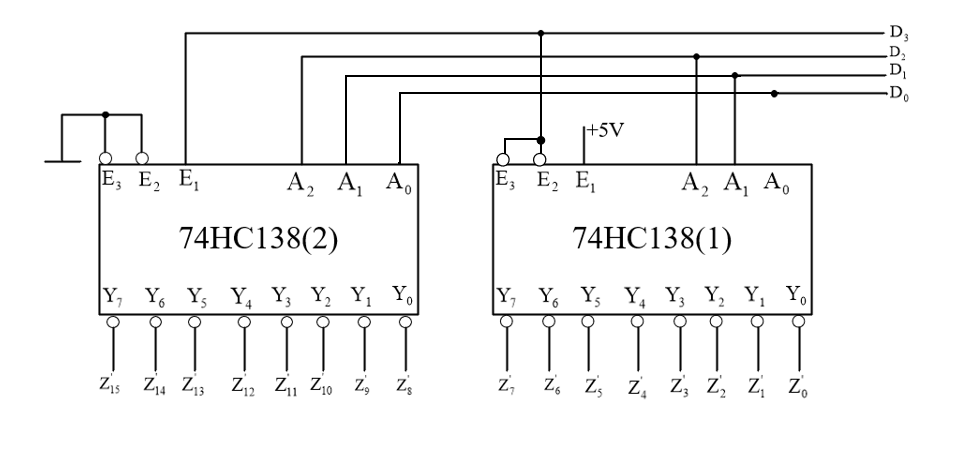

(2)构成4线-16线译码器

与8线-3线优先编码器相似,两个8线-3线优先编码器可以组成一个16线-4线优先编码器,两个3线-8线译码器可以组成一个4线-16线译码器。

在上图中,有两个74HC138芯片,当为1时,对于1号芯片,此时

为0、

为0、

为0,而对于2号74HC138芯片,

为1,

为1,

为1,此时芯片的输出在将1000~1111译码为8~15;当

为0时,对于1号芯片,此时

为1、

为1、

为1,对于2号74HC138芯片,

为0、

为0、

为0时,此时芯片的输出在将0000~0111译码为0~7。

(3)利用74HC138实现和与门之间实现逻辑函数之间的加法Y=AB+AC

由于Y=AB+AC=AB'C+ABC'+ABC,转换为最小项之和为,对于右边内容可以化简为:

,因此可以得到如下所示的电路图:

(4)利用74HC138来完成加法器

如下所示为加法器的原理图:

其中为被加数,

为加数,

来自低位的进位,

是相加后的二进制,

是向高位的进位信号,

列出真值表得:

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

通过真值表的内容可以归纳出逻辑式为:

电路图如下所示:

)