三星电子即将在今年推出一项革命性技术,允许在CPU或GPU上堆叠高带宽内存(HBM),根据韩国经济日报的报道,这一消息在圣何塞举办的三星晶圆代工论坛2024上公布,并得到业内消息人士证实。这项3D封装技术为2025年至2026年间HBM4的集成奠定了基础,不过目前尚不清楚三星今年将采用哪种类型的内存进行封装。

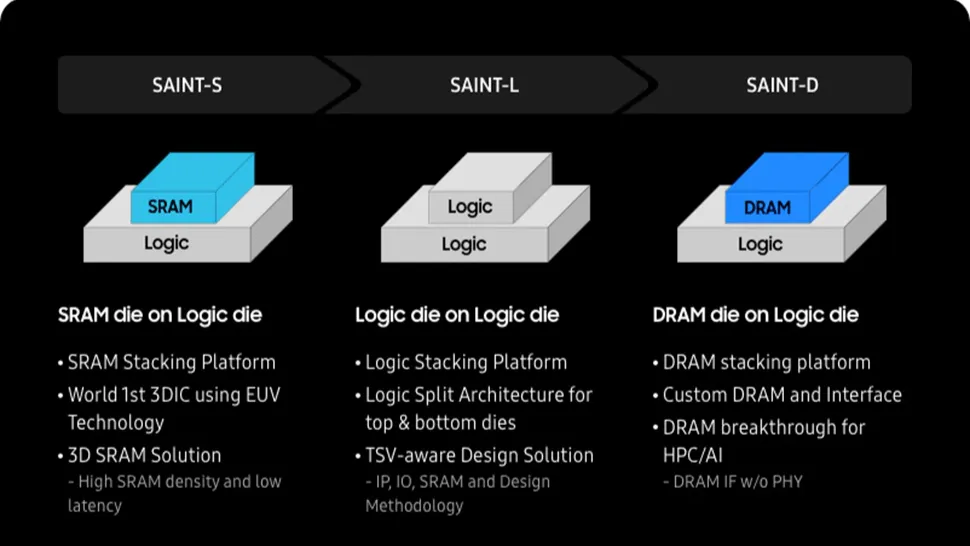

三星的3D封装技术平台称为SAINT(Samsung Advanced Interconnect Technology),包含三种不同的3D堆叠技术:SAINT-S针对SRAM,SAINT-L针对逻辑芯片,而SAINT-D则专注于在逻辑芯片如CPU或GPU顶部堆叠DRAM。三星多年来一直在研发SAINT-D技术(并在2022年正式宣布),现在看来该技术将于今年步入商业化,这对全球最大的内存制造商及领先的晶圆代工厂而言,是一个重要的里程碑。

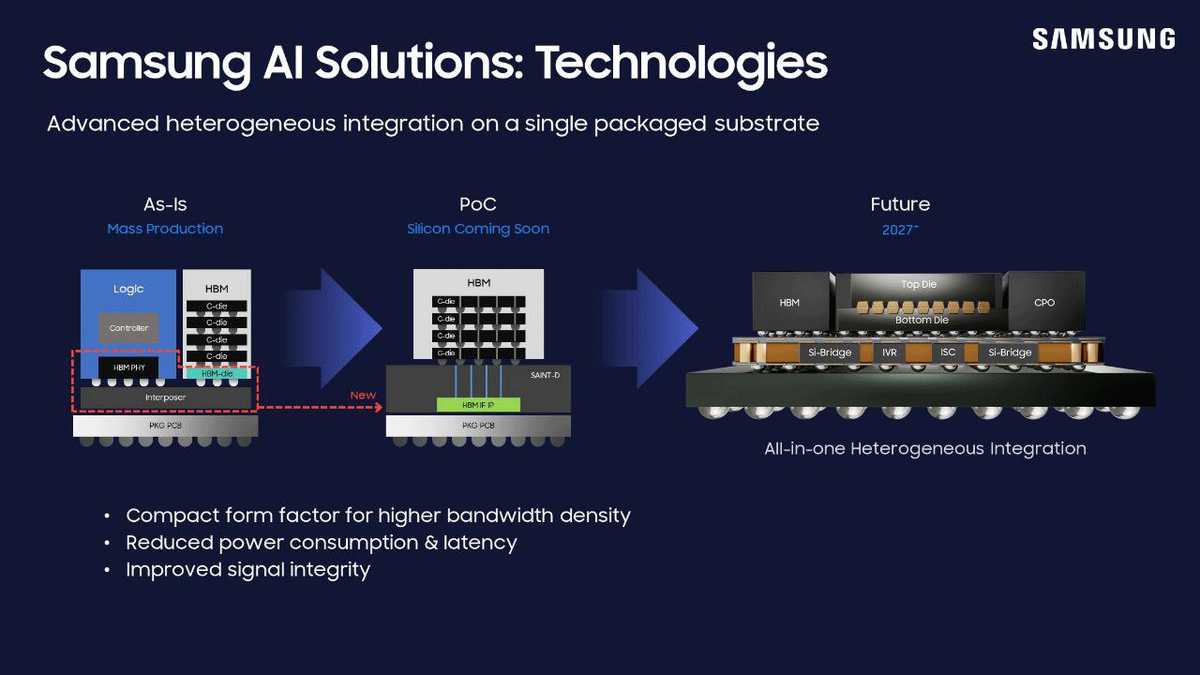

与现有的通过硅中介层水平连接HBM和GPU的2.5D技术不同,三星的新3D封装方法涉及在处理器顶部垂直堆叠HBM芯片。这种垂直堆叠方式免除了硅中介层的需求,但需要使用高级工艺技术制造HBM内存的新型基底芯片。3D封装技术为HBM带来了显著好处,包括更快的数据传输速度、更干净的信号、更低的功耗以及更低的延迟,尽管封装成本相对较高。三星计划将这一先进的3D HBM封装作为一站式服务提供,其内存业务部门负责生产HBM芯片,而晶圆代工业务则为无晶圆厂公司组装实际的处理器。

目前尚不明朗的是三星今年通过SAINT-D具体打算推出什么。在逻辑芯片上放置HBM需要相应的芯片设计,而我们目前并未了解到有任何知名公司计划在2024年至2025年上半年推出设计有顶部堆叠HBM的处理器。

展望未来,三星的目标是在2027年前推出全集成异构技术,这一未来技术将能够集成两层逻辑芯片、通过中介层连接的HBM内存,甚至是共封装光学(CPO)技术,进一步推动高性能计算和数据中心应用的界限。