一、在Matlab中求数据序列的FFT

FFT测试数据生成:包含实部与虚部(虚部为0);

参数设置:

| 参数 | 配置 |

|---|---|

| 采样频率 | 50MHz |

| 信号长度 | 1024 点 |

| 测试信号 | 5MHz与8MHz正弦波的混合信号 |

| 量化方式 | 二进制数:16位有符号数、保留6位小数 |

生成FFT测试数据的Matlab代码:

2024.11.22更改,增加:保存Vivado缩放相对应的FFT的实部和虚部结果:

%% 求特定序列的FFT% 定义参数clear all;clc;Fs = 50e6; % 采样频率 (50MHz)T = 1/Fs; % 采样周期 (s)L = 1024; % 信号长度t = (0:L-1)*T; % 时间向量%% 生成信号 (5MHz 的正弦波和 8MHz 的正弦波的叠加)f1 = 5e6; % 信号频率(5MHz)f2 = 8e6; % 信号频率(8MHz)S = round((0.5*sin(2*pi*f1*t) + sin(2*pi*f2*t))*(2^14-1)); % 取整数%% 对信号进行 FFTY = fft(S);% 计算双边频谱P2 = abs(Y/L);% 计算单边频谱P1 = P2(1:L/2+1);P1(2:end-1) = 2*P1(2:end-1);% 定义频率域f = Fs*(0:(L/2))/L; % 单边谱频率坐标f2 = Fs*(0:L-1)/L; % 双边谱频率坐标% 绘制信号的单边幅度谱figure;plot(f2, P2);title('双边振幅谱');xlabel('f (Hz)');ylabel('|P1(f)|');%% 写入txt文件% 打开文件file1 = fopen('data.txt', 'w');q = quantizer([16 0]); % 量化方式:16位有符号数,0位小数% 写入数据for i = 1:size(S,2)S_bin = num2bin(q, S(i));fprintf(file1, '%s\n', S_bin);end% 关闭文件fclose(file1);% 打开文件file2 = fopen('fft_data_R.txt', 'w');% 写入数据for i = 1:size(Y,2)fprintf(file2, '%d\n', round(real(Y(i))/2^8)); % FFT结果右移8位,与Vivado仿真缩放因子对应end% 关闭文件fclose(file2);% 打开文件file3 = fopen('fft_data_I.txt', 'w');% 写入数据for i = 1:size(Y,2)fprintf(file3, '%d\n', round(imag(Y(i))/2^8)); % FFT结果右移8位,与Vivado仿真缩放因子对应end% 关闭文件fclose(file3);%% 求特定序列的IFFTS_reconstructed = ifft(Y);% 对比原始信号与恢复信号figure;plot(t, S);hold on;plot(t, real(S_reconstructed), '--');legend('原始信号', '恢复信号');title('原始信号与恢复信号对比');xlabel('时间 (s)');ylabel('幅度');

经FFT后的测试信号的双边谱:

测试信号和经IFFT还原后的信号:

二、在Vivado中求数据序列的FFT和IFFT

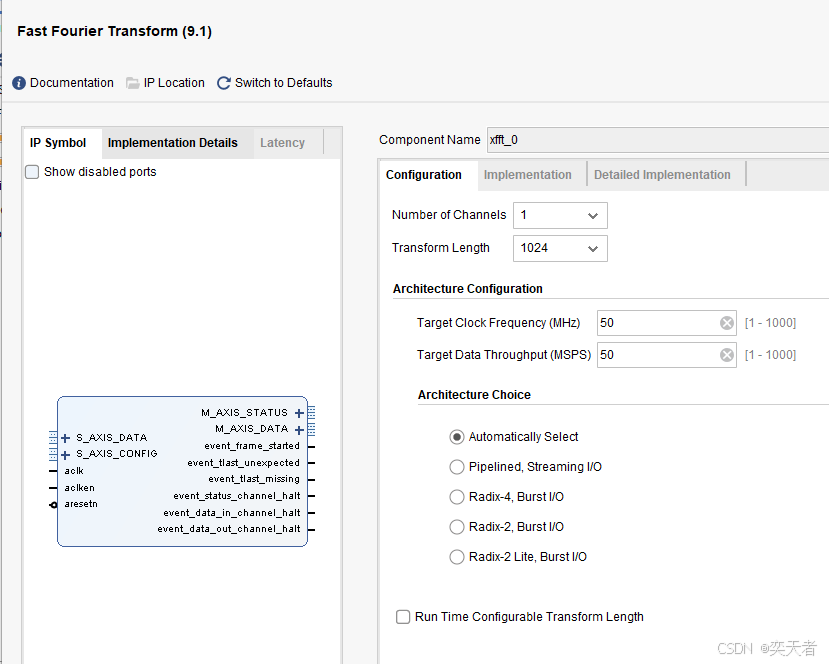

2.1 FFT的IP核参数设置

重要参数说明:

| 参数 | 配置 |

|---|---|

| Transform Length(FFT变换长度) | 1024点 |

| Target Clock Frequency(目标时钟频率) | 50MHz |

| Target Data Throughput(目标数据吞吐率) | 50MSPS |

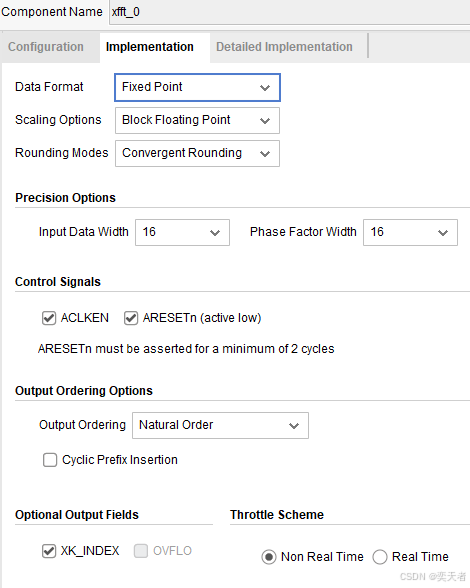

| Scaling Options(缩放设置) | 选择Block Floating Point,由IP核决定如何缩放 |

| Input Data Width(输入数据位宽) | 16 |

| Output Ordering(输出排序) | 选择Natural Order(注:选择Bit/Digit Reversed Order,输出信号会逆序;此处选择顺序输出) |

参数设置界面一:

参数设置界面二:

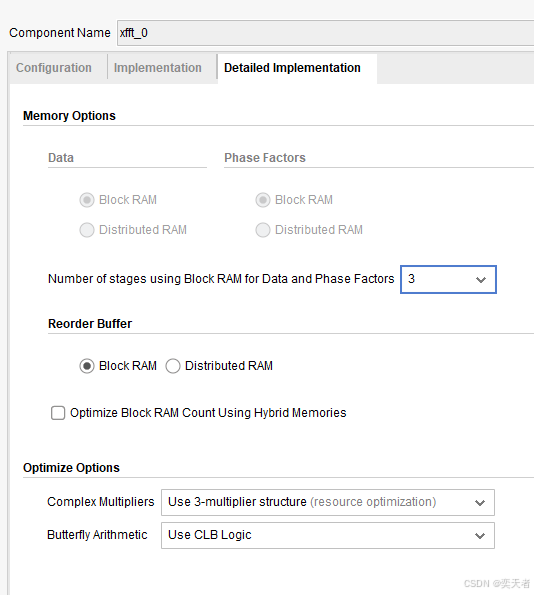

参数设置界面三:

2.2 求数据序列的FFT

s_axis_config_tdata: 配置数据输入,8位(前七位填充为0);

仅有FWD/INV:可选择当FWD_INV = 1时,计算正向变换(FFT)。如果FWD_INV = 0,则计算逆变换(IFFT)。

s_axis_data_tdata: 待输入数据,32位;

输入高16位为虚部,低16位为实部。

m_axis_data_tdata: 输出经FFT后的数据,32位;

输出高16位为虚部,低16位为实部。

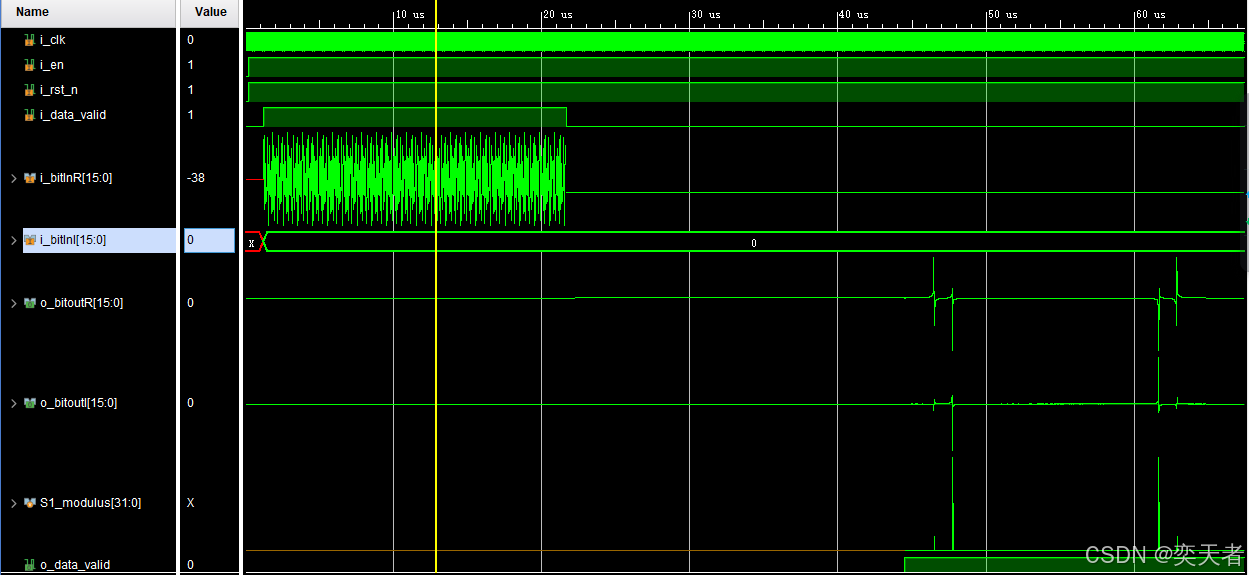

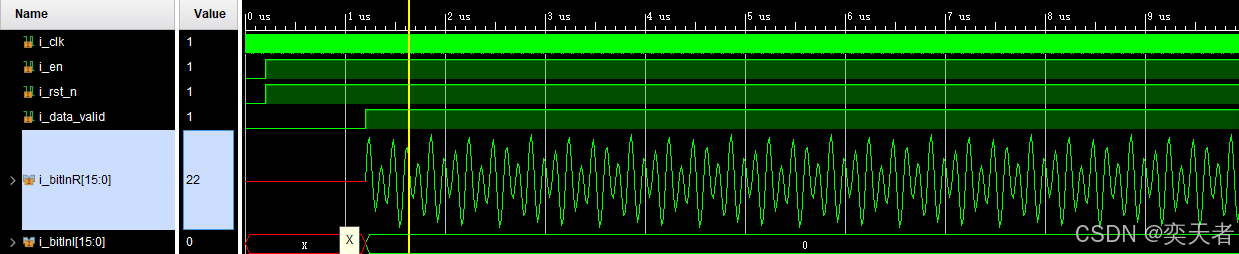

仿真图如下:

其中S1_modulus为输出FFT数据实部和虚部的平方和,verilog无求平方根函数,此处近似替代。

FFT的verilog代码如下:

module FFT_Test(i_clk,i_en,i_rst_n,i_data_valid,i_bitInR,i_bitInI,o_bitoutR,o_bitoutI,o_data_valid,o_rec_bitR,o_rec_bitI,o_rec_valid

);parameter WIDTH = 16;input i_clk; // 系统时钟:50MHzinput i_en; // FFT的IP核时钟使能input i_rst_n; // 复位信号,低电平有效input i_data_valid; // 输入待FFT的信号有效input signed [WIDTH-1:0] i_bitInR; // 输入信号实部input signed [WIDTH-1:0] i_bitInI; // 输入信号虚部output reg signed [WIDTH-1:0] o_bitoutR; // 经过FFT的信号实部output reg signed [WIDTH-1:0] o_bitoutI; // 经过FFT的信号虚部output reg o_data_valid; // 输出FFT信号有效output reg [WIDTH-1:0] o_rec_bitR; // 输出经IFFT的还原信号实部output reg [WIDTH-1:0] o_rec_bitI; // 输出经IFFT的还原信号实部output reg o_rec_valid; // 还原信号有效// 配置通道wire [7:0] s_axis_config_tdata;reg s_axis_config_tvalid;wire s_axis_config_tready;// 输入数据通道wire s_axis_data_tready;reg [2*WIDTH-1:0] s_axis_data_tdata;reg s_axis_data_tvalid;reg s_axis_data_tlast;// 输出数据通道wire m_axis_data_tready;wire m_axis_data_tvalid, m_axis_data_tlast;wire [2*WIDTH-1:0] m_axis_data_tdata;wire [23:0] m_axis_data_tuser;// 状态通道wire m_axis_status_tready;wire [7:0] m_axis_status_tdata;wire m_axis_status_tvalid;// 事件标志输出wire event_frame_started, event_tlast_unexpected, event_tlast_missing;wire event_status_channel_halt, event_data_in_channel_halt, event_data_out_channel_halt;xfft_0 fft_0 (.aclk(i_clk), // input wire aclk.aclken(i_en), // input wire aclken.aresetn(i_rst_n), // input wire aresetn.s_axis_config_tdata(s_axis_config_tdata), // input wire [7 : 0] s_axis_config_tdata.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid.s_axis_config_tready(s_axis_config_tready), // output wire s_axis_config_tready.s_axis_data_tdata(s_axis_data_tdata), // input wire [31 : 0] s_axis_data_tdata.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready.s_axis_data_tlast(s_axis_data_tlast), // input wire s_axis_data_tlast.m_axis_data_tdata(m_axis_data_tdata), // output wire [31 : 0] m_axis_data_tdata.m_axis_data_tuser(m_axis_data_tuser), // output wire [23 : 0] m_axis_data_tuser.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid.m_axis_data_tready(m_axis_data_tready), // input wire m_axis_data_tready.m_axis_data_tlast(m_axis_data_tlast), // output wire m_axis_data_tlast.m_axis_status_tdata(m_axis_status_tdata), // output wire [7 : 0] m_axis_status_tdata.m_axis_status_tvalid(m_axis_status_tvalid), // output wire m_axis_status_tvalid.m_axis_status_tready(m_axis_status_tready), // input wire m_axis_status_tready.event_frame_started(event_frame_started), // output wire event_frame_started.event_tlast_unexpected(event_tlast_unexpected), // output wire event_tlast_unexpected.event_tlast_missing(event_tlast_missing), // output wire event_tlast_missing.event_status_channel_halt(event_status_channel_halt), // output wire event_status_channel_halt.event_data_in_channel_halt(event_data_in_channel_halt), // output wire event_data_in_channel_halt.event_data_out_channel_halt(event_data_out_channel_halt) // output wire event_data_out_channel_halt);// FFT的IP核设置

// wire [9:0] SCALE_SCH; // 缩放因子 [1 0 2 3 2]

// assign SCALE_SCH = 10'b00_00_00_00_10;

// assign s_axis_config_tdata = {5'd0,SCALE_SCH,1'b1}; // 设置为FFTassign s_axis_config_tdata = 8'd1; // 设置为FFTassign m_axis_data_tready = 1'b1; // 输出一直有效assign m_axis_status_tready = 1'b1; // 输出一直有效// s_axis_config_tvalidalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_config_tvalid <= 1'b0;else if(s_axis_config_tready) begins_axis_config_tvalid <= 1'b1;end// data_numreg [10:0] data_num;always@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)data_num <= 11'd0;else if(i_data_valid) beginif(data_num == 11'd1023)data_num <= 11'd0;elsedata_num <= data_num + 1'b1;endelsedata_num <= data_num;// s_axis_data_tvalidalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_data_tvalid <= 1'b0;else if(i_data_valid) beginif(s_axis_data_tready)s_axis_data_tvalid <= 1'b1;endelses_axis_data_tvalid <= 1'b0;// s_axis_data_tdataalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_data_tdata <= 32'd0;else if(i_data_valid) begins_axis_data_tdata <= {i_bitInI,i_bitInR}; // 输入高16位为虚部,低16位为实部;end// s_axis_data_tlastalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_data_tlast <= 1'b0;else beginif(data_num == 11'd1023)s_axis_data_tlast <= 1'b1;elses_axis_data_tlast <= 1'b0;end// o_bitoutI,o_bitoutRalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n) begino_bitoutI <= 16'd0;o_bitoutR <= 16'd0;endelse if(m_axis_data_tvalid) begino_bitoutI <= m_axis_data_tdata[2*WIDTH-1:WIDTH]; // 输出高16位为虚部o_bitoutR <= m_axis_data_tdata[WIDTH-1:0]; // 输出低16位为实部endelse begino_bitoutI <= 16'd0;o_bitoutR <= 16'd0;end// o_data_validalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)o_data_valid <= 1'b0;else if(m_axis_data_tvalid)o_data_valid <= 1'b1;else if(m_axis_data_tlast)o_data_valid <= 1'b0;// 续IFFT代码,下文

2.3 求数据序列的IFFT

s_axis_config_tdata2: 配置数据输入,8位(前七位填充为0);

仅有FWD/INV:可选择当FWD_INV = 1时,计算正向变换(FFT)。如果FWD_INV = 0,则计算逆变换(IFFT)。

s_axis_data_tdata2: 待输入数据,32位;

输入高16位为虚部,低16位为实部。此处输入上一步输出的FFT数据。

m_axis_data_tdata2: 输出经FFT后的数据,32位;

输出高16位为虚部,低16位为实部。此处输出为经IFFT还原后的信号。

仿真图如下:

输入测试信号

对上一步FFT数据经IFFT还原后的信号:(此处实部与输入实部基本一致;虚部相对较小,可忽略)

IFFT的verilog代码如下:

// 续上文FFT代码,为完整代码// 配置通道wire [7:0] s_axis_config_tdata2;reg s_axis_config_tvalid2;wire s_axis_config_tready2;// 输入数据通道wire s_axis_data_tready2;reg [2*WIDTH-1:0] s_axis_data_tdata2;reg s_axis_data_tvalid2;reg s_axis_data_tlast2;// 输出数据通道wire m_axis_data_tready2;wire m_axis_data_tvalid2, m_axis_data_tlast2;wire [2*WIDTH-1:0] m_axis_data_tdata2;wire [23:0] m_axis_data_tuser2;// 状态通道wire m_axis_status_tready2;wire [7:0] m_axis_status_tdata2;wire m_axis_status_tvalid2;// 事件标志输出wire event_frame_started2, event_tlast_unexpected2, event_tlast_missing2;wire event_status_channel_halt2, event_data_in_channel_halt2, event_data_out_channel_halt2;xfft_0 ifft_0 (.aclk(i_clk), // input wire aclk.aclken(i_en), // input wire aclken.aresetn(i_rst_n), // input wire aresetn.s_axis_config_tdata(s_axis_config_tdata2), // input wire [7 : 0] s_axis_config_tdata.s_axis_config_tvalid(s_axis_config_tvalid2), // input wire s_axis_config_tvalid.s_axis_config_tready(s_axis_config_tready2), // output wire s_axis_config_tready.s_axis_data_tdata(s_axis_data_tdata2), // input wire [31 : 0] s_axis_data_tdata.s_axis_data_tvalid(s_axis_data_tvalid2), // input wire s_axis_data_tvalid.s_axis_data_tready(s_axis_data_tready2), // output wire s_axis_data_tready.s_axis_data_tlast(s_axis_data_tlast2), // input wire s_axis_data_tlast.m_axis_data_tdata(m_axis_data_tdata2), // output wire [31 : 0] m_axis_data_tdata.m_axis_data_tuser(m_axis_data_tuser2), // output wire [23 : 0] m_axis_data_tuser.m_axis_data_tvalid(m_axis_data_tvalid2), // output wire m_axis_data_tvalid.m_axis_data_tready(m_axis_data_tready2), // input wire m_axis_data_tready.m_axis_data_tlast(m_axis_data_tlast2), // output wire m_axis_data_tlast.m_axis_status_tdata(m_axis_status_tdata2), // output wire [7 : 0] m_axis_status_tdata.m_axis_status_tvalid(m_axis_status_tvalid2), // output wire m_axis_status_tvalid.m_axis_status_tready(m_axis_status_tready2), // input wire m_axis_status_tready.event_frame_started(event_frame_started2), // output wire event_frame_started.event_tlast_unexpected(event_tlast_unexpected2), // output wire event_tlast_unexpected.event_tlast_missing(event_tlast_missing2), // output wire event_tlast_missing.event_status_channel_halt(event_status_channel_halt2), // output wire event_status_channel_halt.event_data_in_channel_halt(event_data_in_channel_halt2), // output wire event_data_in_channel_halt.event_data_out_channel_halt(event_data_out_channel_halt2) // output wire event_data_out_channel_halt);// IFFT的IP核设置

// assign s_axis_config_tdata2 = {5'd0,SCALE_SCH,1'b0}; // 设置为IFFTassign s_axis_config_tdata2 = 8'd0; // 设置为IFFTassign m_axis_data_tready2 = 1'b1; // 输出一直有效assign m_axis_status_tready2 = 1'b1; // 输出一直有效// s_axis_config_tvalid2always@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_config_tvalid2 <= 1'b0;else if(s_axis_config_tready2) begins_axis_config_tvalid2 <= 1'b1;end// data_num2reg [10:0] data_num2;always@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)data_num2 <= 11'd0;else if(m_axis_data_tvalid) beginif(data_num2 == 11'd1023)data_num2 <= 11'd0;elsedata_num2 <= data_num2 + 1'b1;endelsedata_num2 <= 11'd0;// s_axis_data_tvalid2always@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_data_tvalid2 <= 1'b0;else if(m_axis_data_tvalid) beginif(s_axis_data_tready2)s_axis_data_tvalid2 <= 1'b1;endelses_axis_data_tvalid2 <= 1'b0;// s_axis_data_tdata2always@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_data_tdata2 <= 32'd0;else if(m_axis_data_tvalid) begins_axis_data_tdata2 <= m_axis_data_tdata; // 输入高16位为虚部,低16位为实部;end// s_axis_data_tlast2always@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)s_axis_data_tlast2 <= 1'b0;else beginif(data_num2 == 11'd1023)s_axis_data_tlast2 <= 1'b1;elses_axis_data_tlast2 <= 1'b0;end// o_rec_bitI,o_rec_bitRalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n) begino_rec_bitI <= 16'd0;o_rec_bitR <= 16'd0;endelse if(m_axis_data_tvalid2) begino_rec_bitI <= m_axis_data_tdata2[2*WIDTH-1:WIDTH]; // 输出高16位为虚部o_rec_bitR <= m_axis_data_tdata2[WIDTH-1:0]; // 输出低16位为实部endelse begino_rec_bitI <= 16'd0;o_rec_bitR <= 16'd0;end// o_rec_validalways@(posedge i_clk or negedge i_rst_n)if(!i_rst_n)o_rec_valid <= 1'b0;else if(m_axis_data_tvalid2)o_rec_valid <= 1'b1;else if(m_axis_data_tlast2)o_rec_valid <= 1'b0;endmodule

2.4 testbench文件

仿真文件(verilog代码)如下:

module FFT_Test_tb();parameter WIDTH = 16;reg i_clk;reg i_en;reg i_rst_n;reg i_data_valid;reg signed [WIDTH-1:0] i_bitInR;reg signed [WIDTH-1:0] i_bitInI;wire [WIDTH-1:0] o_bitoutR;wire [WIDTH-1:0] o_bitoutI;wire o_data_valid;wire [WIDTH-1:0] o_rec_bitR;wire [WIDTH-1:0] o_rec_bitI;wire o_rec_valid;FFT_Test FFT_Test(.i_clk(i_clk),.i_en(i_en),.i_rst_n(i_rst_n),.i_data_valid(i_data_valid),.i_bitInR(i_bitInR),.i_bitInI(i_bitInI),.o_bitoutR(o_bitoutR),.o_bitoutI(o_bitoutI),.o_data_valid(o_data_valid),.o_rec_bitR(o_rec_bitR),.o_rec_bitI(o_rec_bitI),.o_rec_valid(o_rec_valid));parameter Clk_Period = 20; //50MHzparameter Clk_HalfPeriod = Clk_Period/2;parameter Data_Period = Clk_Period; //50MHzparameter Data_num = 1024; //数据长度parameter Time_sim = Data_num*Data_Period; //仿真时间initial i_clk = 1;always #Clk_HalfPeriod i_clk = ~i_clk;reg [2*WIDTH-1:0] S1_modulus, S2_modulus;integer count;reg [WIDTH-1:0] memory[0:Data_num-1];integer fp_w1;integer fp_w2;integer fp_w3;integer fp_w4;initial begini_rst_n = 0;i_en = 0;i_data_valid = 0;#200;i_en = 1;i_rst_n = 1;#1000;i_data_valid = 1;// $readmemb("D:/Vivado_Exp/00_Test/FFT_Test/data.txt", memory);$readmemb("../../../../data.txt", memory);count = 0;repeat(Data_num) begini_bitInR = memory[count];i_bitInI = 16'd0; // 16'd0;count = count + 1;#Data_Period;endi_data_valid = 0;@(posedge o_data_valid);fp_w1 = $fopen("../../../../fft_data_R2.txt","w");fp_w2 = $fopen("../../../../fft_data_I2.txt","w");#1;repeat(Data_num) begin$fwrite(fp_w1, "%d\n", $signed(o_bitoutR));$fwrite(fp_w2, "%d\n", $signed(o_bitoutI));S1_modulus = $signed(o_bitoutR) * $signed(o_bitoutR) + $signed(o_bitoutI) * $signed(o_bitoutI);#Data_Period;end$fclose(fp_w1);$fclose(fp_w2);fp_w3 = $fopen("../../../../ifft_data_R2.txt","w");fp_w4 = $fopen("../../../../ifft_data_I2.txt","w");@(posedge o_rec_valid);#1;repeat(Data_num) begin$fwrite(fp_w3, "%d\n", $signed(o_rec_bitR));$fwrite(fp_w4, "%d\n", $signed(o_rec_bitI));S2_modulus = $signed(o_rec_bitR) * $signed(o_rec_bitR) + $signed(o_rec_bitI) * $signed(o_rec_bitI);#Data_Period;end$fclose(fp_w3);$fclose(fp_w4);#50_000;$stop;endendmodule

2.5 求数据序列的IFFT

2024.11.22更改,增加:验证FFT的实部和虚部结果的正确性:

Matlab的计算FFT的实部结果(图片左侧为序号86-112的FFT实部结果,保存在fft_data_R.txt文件夹中):

Vivado的计算FFT的实部结果(图片右侧为序号86-112的FFT实部结果,保存在fft_data_R2.txt文件夹中):

Matlab的计算FFT的虚部结果(图片左侧为序号86-112的Matlab的FFT虚部结果,保存在fft_data_I.txt文件夹中):

Vivado的计算FFT的虚部结果(图片右侧为序号86-112的Vivado的FFT虚部结果,保存在fft_data_I2.txt文件夹中):

可见,Matlab和Vivado的FFT计算结果基本一致。

增加说明:Vavido的FFT仿真中,FFT的IP输出块指数(BLK_EXP)为8,表示将未缩放的FFT计算结果右移8位后输出到m_axis_data_tdata,(可通过IP核输出的m_axis_status_tdata端口查看)。

三、总结

本文介绍了Vivado中FFT的IP核用法,先用Matlab生成待测试数据;在Vivado中配置FFT的IP核,实现求测试数据的FFT结果并通过IFFT还原测试数据,验证结果基本一致。

FFT的IP核参数介绍可参考:

[Vivado] IP核学习之Fast Fourier Transform