提示:本文基于 MIPI Specification for D-PHY Version 1.2 – 01 August 2014

文章目录

- 简介

- D-PHY 概述

- PHY 功能概述

- 体系结构

- Lane 模块

- 主机和从机

- 高频时钟产生

- 时钟通道、数据通道和物理协议接口

- 可选择的通道选项

- Global Operation

- Transmission Data Structure

- Data Units

- Bit Order, Serialization, and De-Serialization

- Encoding, Decoding, Mapping and De-Mapping

- Data Buffering

- Lane States and Line Levels

- Operating Modes: Control, High-Speed, and Escape

- High-Speed Data Transmission

- Burst Payload Data

- Start-of-Transmission

- End-of-Transmission

- HS Data Transmission Burst

- Bi-Directional Lane Turnaround

- Escape Mode

- Remote Triggers

- Low-Power Data Transmission

- Ultra-Low Power State

- Escape Mode State Machine

- High-Speed Clock Transmission

- Clock Lane Ultra-Low Power State

- Global Operation Timing Parameters

- Global Operation Flow Diagram

简介

该规范为移动设备内部组件之间的通信互连提供了灵活、低成本、高速的串行接口解决方案。传统上,由于 EMI 的原因,这些接口是 CMOS 并行总线,具有低比特率。D-PHY 解决方案可以为更高级的应用程序显著扩展接口带宽。D-PHY 解决方案可以以非常低的功耗实现。

D-PHY 概述

D-PHY 描述了一种源同步、高速、低功耗、低成本的 PHY,特别适合于移动应用。该 D-PHY 规范主要用于将摄像机和显示器连接到主机处理器。当然,它也可以应用于许多其他应用程序。按照设想,在更通用的通信网络中,同样类型的 PHY 也将用于双工配置的互连。由于链路两端的主从关系,链路的操作速率和可用数据速率是不对称的。非对称设计大大降低了连接的复杂性。一些功能,如双向,半双工操作是可选的。对于具有非对称数据流量需求的应用程序,以及当返回通道的单独互连成本过高时,利用此特性非常有吸引力。虽然此特性是可选的,但对于没有返回通信需求或希望应用物理上不同的返回通信通道的应用程序,它避免了强制性的开销。

PHY 功能概述

D-PHY 提供主从之间的同步连接。一个实用的 PHY 配置由一个时钟信号和一个或多个数据信号组成。时钟信号是单向的,起源于主站,终止于从站。根据所选的选项,数据信号可以是单向的,也可以是双向的。对于半双工工作,反向带宽是正向带宽的四分之一。令牌传递用于控制链路的通信方向。

链路包括用于快速数据流量的高速信号模式和用于控制目的的低功耗信号模式。可选地,低功耗 Escape 模式可用于低速异步数据通信。高速数据通信以具有任意数量的有效载荷数据字节的突发形式出现。

PHY 每个数据通道使用两根线,时钟通道使用两根线。因此最小 PHY 配置需要四根线。在高速模式下,每个 Lane 在两侧端接,并由低摆幅差分信号驱动。在低功耗模式下,所有的线都是单端和非端接的。为了最小化 EMI,该模式的驱动器应采用慢速控制和电流限制。

高速模式下的最大可实现比特率是由发送器、接收器和互连实现的性能决定的。因此,在本文档中没有规定最大比特率。然而,本规范主要旨在定义一种比特率范围为 80 至 1500 Mbps / Lane 的解决方案,该解决方案是没有校准的情况下。在有校准的情况下,具有高达 2500 Mbps 的数据速率。当 DUT 支持大于 1500 Mbps 的数据速率时,还应支持桌面功能。尽管 PHY 配置并不局限于这个范围,但实际的限制使其成为预期应用程序最合适的范围。对于固定的时钟频率,可以通过使用更多的 Lanes 来增加 PHY 配置的可用数据容量。采用突发模式通信可以降低有效数据吞吐量。低功耗模式下最大数据速率为 10 Mbps。

体系结构

本节介绍物理层的内部结构,包括物理层在行为层的功能。此外,还给出了几种可能的 PHY 配置。每个配置都可以看作是一组基本模块的合适组合。

Lane 模块

一个 PHY 配置由一个时钟通道模块和一个或多个 Lane 模块组成。每个 PHY Lane 模块通过两条线路与 Lane Interconnect 另一侧的互补部分通信。

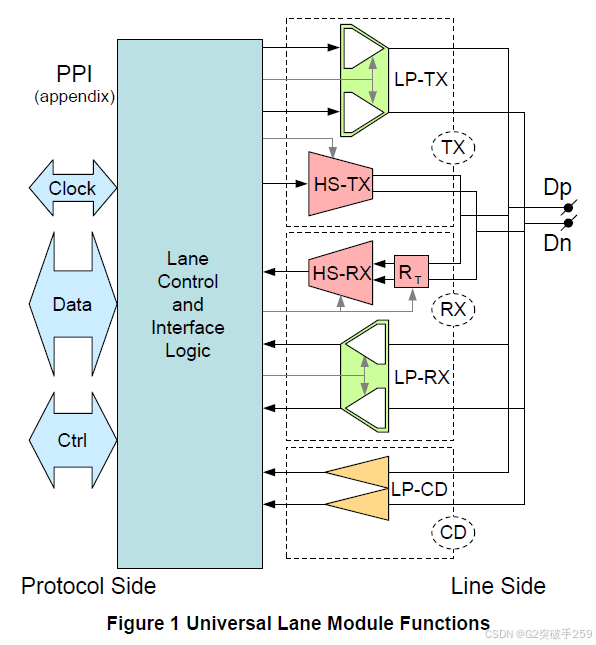

每个 Lane 模块由一个或多个差分高速功能组成,同时利用两根互连线,一个或多个单端低功耗功能分别在每根互连线上运行,以及控制和接口逻辑。图 1 显示了所有功能的概述。高速信号具有低电压摆幅,例如 200mv,而低功耗信号具有大电压摆幅,例如 1.2v。High Speed 功能用于高速数据传输。Low Power 功能主要用于控制,但也有其他可选的用例。I/O 功能由 Lane Control 和 Interface Logic 块控制。该模块与上层协议单元连接,并决定 Lane 模块的全局操作。

高速功能包括一个差分发射器(HS-TX)和一个差分接收器(HS-RX)。

一个 Lane 模块可以包含一个 HS-TX,一个 HS-RX,或者两者都包含。如果一个 Lane 模块同时包含 HS-TX 和 HS-RX,在正常工作时,它们不会同时启用。启用的高速功能应在第 9.1.1 节和第 9.2.1 节中定义的 Lane 互连的其一侧终止 Lane。如果 Lane 模块中的高速功能未启用,则该功能应置于高阻抗状态。

低功耗功能包括单端发送器(LP-TX)、接收器(LP-RX)和低功耗竞争检测器(LP-CD)。低功耗功能总是成对出现,因为它们是单端功能,分别在两条互连线上运行。

高速和低功耗功能的存在是相关的。也就是说,如果一个 Lane 模块包含一个 HS-TX,那么它也应该包含一个 LP-TX。HS-RX 和 LP-RX 也存在类似的约束。

如果包含 LP-RX 的 Lane 模块通电,则该 LP-RX 应始终处于活动状态并持续监控 Line 电平。只有在驱动低功耗状态时才使能 LP-TX。只有双向操作时才需要配置 LP-CD 功能。如果存在,则启用 LP-CD 功能,以在 LP-TX 驱动低功耗状态时检测竞争情况。LP-CD 在线上驱动新状态之前检查竞争,但在 ULPS 中除外。

LP-TX、HS-TX 和 HS-RX 在单个 Lane 模块中的活动是互斥的,除了一些短暂的交叉期。Line-side 信号以及 HS-TX、HS-RX、LP-TX、LP-RX 和 LP-CD 功能的详细规格请参见第 9 节和第 10 节。

为了正常工作,Lane Interconnect 两侧的 Lane 模块中的一组功能必须匹配。这意味着对于通道互连一侧的每个 HS 和 LP 发送或接收功能,必须在另一侧存在互补的 HS 或 LP 接收或发送功能。此外,在结合 TX 和 RX 功能的任何 Lane 模块中都需要一个竞争检测器。

主机和从机

每个链路都有一个主机和一个从机。主机向时钟通道提供高速 DDR 时钟信号,是主数据源。从机在时钟通道接收时钟信号,是主数据接收器。数据通信的主要方向,从源到接收,称为前向。相反方向的数据通信称为反向传输。只有双向数据通道可以反向传输。在所有情况下,时钟通道保持在前向,但双向数据通道可以反转,从从机获取数据。

高频时钟产生

在许多情况下,锁相环时钟乘法器需要在主机端产生高频时钟。D-PHY 规范使用一种体系结构模型,其中 PHY 外部的单独时钟乘法器单元为 PHY 生成所需的高频时钟信号。这个时钟乘法器在实际中是否集成在物理层中留给实现者控制。

时钟通道、数据通道和物理协议接口

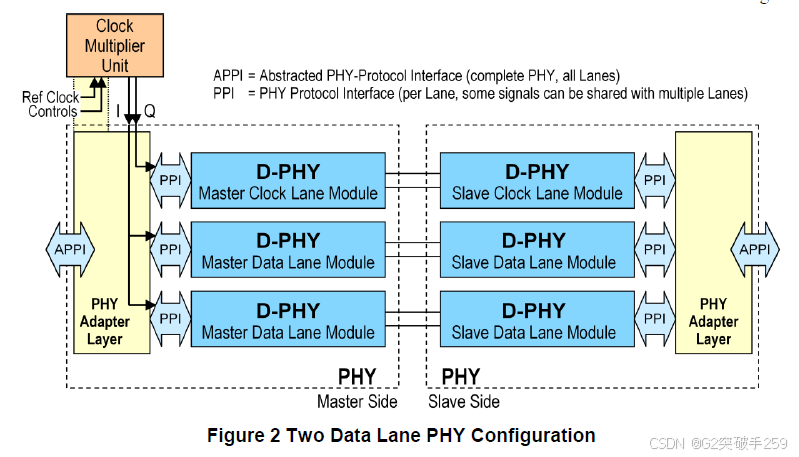

除了 Lane 模块之外,一个完整的链路还包含一个将所有 Lane、时钟乘法器单元和物理协议接口连接在一起的 PHY 适配器层。图 2 显示了具有两个数据通道和一个单独时钟乘法器单元的链路的 PHY 配置示例。PHY 适配器层虽然是 PHY 的一个组件,但不在本规范的范围内。

每个通道的逻辑物理协议接口(PPI)包括一组覆盖该通道功能的信号。如图 2 所示,时钟信号可以在所有通道上共享。时钟乘法器单元的参考时钟和控制信号不在本规范的范围内。

可选择的通道选项

一个 PHY 配置由一个时钟 Lane 和一个或多个数据 Lane 组成。所有通道应支持前向高速传输和 Escape 模式。

有两种主要类型的数据通道:

- 双向(具有反转和一些反向通信功能)

- 单向(没有反转或任何类型的反向通信功能)

双向数据通道应包括以下一种或两种反向通信选项:

- 高速反向数据通信

- 低功耗反向 Escape 模式(包括或不包括 LPDT)

所有通道都应包括对前向 ULPS 和触发器的 Escape 模式支持。其他 Escape 模式功能是可选的;所有可能的 Escape 模式特性将在第 6.6 节中描述。应用程序应定义需要哪些额外的 Escape 模式功能,对于双向通道,应分别为每个方向选择 Escape 模式功能。

这就产生了用于完整 PHY 配置的许多选项。自由度为:

- 单数据通道或多数据通道

- 双向和/或单向数据通道(每通道)

- 支持的反向通信类型(每通道)

- Escape 模式支持的功能(每个方向,每通道)

- 数据传输可以使用 8-bit 原始数据(默认)或使用 8b9b 编码符号(见附件 C)

Global Operation

介绍 D-PHY 的操作,包括信号类型、通信机制、操作模式和编码方案。所需电气功能的详细规格见第 9 节。

Transmission Data Structure

在高速或低功耗传输期间,链路将协议层提供的有效载荷数据传输到链路的另一端。本节规定了传输和接收有效载荷数据的限制。

Data Units

最小有效载荷数据单位应为一个字节。提供给 TX 的数据和从任何 Lane 上的 RX 获取的数据应该是整数字节。这一限制适用于任何方向的高速和低功耗数据传输。

Bit Order, Serialization, and De-Serialization

对于串行传输,数据应在发送 PHY 中序列化,在接收 PHY 中反序列化。PHY 对输入和输出数据没有特定的定义、值或顺序。

Encoding, Decoding, Mapping and De-Mapping

本规范不要求行编码。但如需采用行编码,则按附件 C 执行。

Data Buffering

根据协议请求进行数据传输。一旦通信开始,发送端的协议层只要不停止其传输请求,就应该提供有效的数据。对于使用 Line 编码的 Lane,也可以在传输中插入控制符号。接收端的协议层应在接收 PHY 发送数据后立即接收数据。信号概念,因此 PHY 协议握手,不允许数据节流。为此目的的任何数据缓冲都应该在协议层内。

Lane States and Line Levels

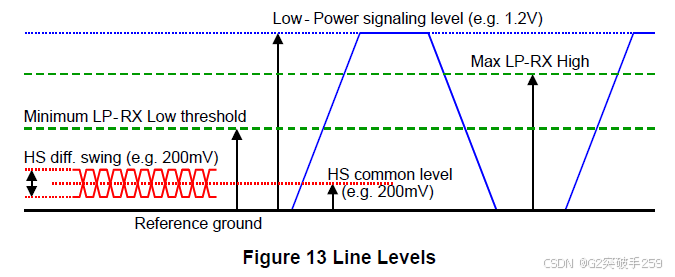

发送端功能通过驱动某些线路电平来决定线路状态。在正常操作期间,HS-TX 或 LP-TX 驱动 Lane。HS-TX 总是差分驱动 Lane。两个 LP-TX 驱动一个 Lane 的两个独立的单 Line。这导致两种可能的高速通道状态:差分 0 和差分 1,和四种可能的低功耗通道状态。低功率通道状态的解释取决于操作模式。LP-Receiver 应始终将两个高速差分状态解释为 LP-00。

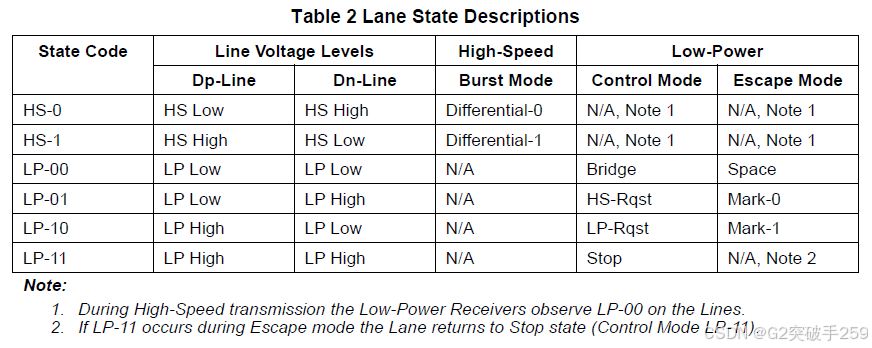

停止状态具有非常排他性和中心的功能。如果 Line 电平在所需的最小时间内显示停止状态,则无论以前的状态如何,PHY 状态机都应返回到停止状态。这可以是 RX 或 TX 模式,取决于最近的操作方向。表 2 列出了在正常运行期间 Lane 上可能出现的所有状态。电气电平的详细规格见第 9 节。

所有 LP 状态周期的持续时间应至少为 tLPX。状态转换应该是平滑的,并排除小故障的影响。时钟信号可以通过 Dp 线和 Dn 线的异环重构来实现。理想情况下,重构的时钟持续时间至少为 2 * tLPX,但由于信号斜率和行程电平的影响,可能具有 50% 以外的占空比。

Operating Modes: Control, High-Speed, and Escape

在正常运行时,通道将处于控制模式或高速模式。高速数据传输以突发的方式进行,从停止状态(LP-11)开始到结束,根据定义,停止状态为控制模式。Lane 仅在数据突发时处于高速模式。进入高速模式的顺序为:LP-11,LP-01,LP-00,此时 Lane 将一直处于高速模式,直到收到 LP-11。Esacpe 模式只能在控制模式下通过请求进入。通道在检测到停止状态(LP-11)后,应始终退出 Esacpe 模式并返回控制模式。如果不在高速或 Esacpe 模式,通道应保持在控制模式。对于数据通道和时钟通道,停止状态作为一般的待机状态,可以持续任何一段时间。从停止状态开始可能发生的事件有:高速数据传输请求(LP-11、LP-01、LP-00)、Esacpe 模式请求(LP-11、LP-10、LP-00、LP-01、LP-00)或转向请求(LP-11、LP-10、LP-00、LP-10、LP-00)。

High-Speed Data Transmission

高速数据传输以突发形式发生。为了帮助接收器同步,数据突发应在发送端以前导和后导序列进行扩展,并在接收端消除。因此,这些前导和后导包头只能在传输线上观察到。

传输从停止状态开始,并以停止状态结束。在突发之间的中间时间内,数据通道应保持停止状态,除非在通道上提出转向或 Escape 请求。在 HS 数据突发期间,时钟通道应处于高速模式,向接收器提供 DDR 时钟。

Burst Payload Data

突发的有效载荷数据应始终表示有效载荷数据字节的整数,最小长度为一个字节。请注意,对于短突发,Start 和 End 开销比实际传输有效载荷数据消耗更多的时间。PHY 没有隐含的最大字节数。然而,在物理层中,在 HS 数据突发期间没有自动的错误恢复方法。实际的错误率几乎为零。重要的是要考虑每个协议的最大突发长度的最佳选择是什么。

Start-of-Transmission

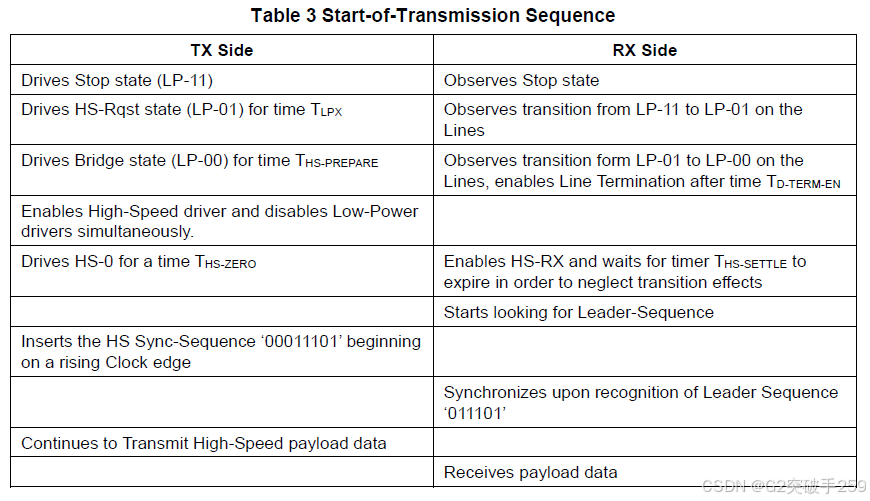

在发送请求后,Lane 离开停止状态,并通过启动传输(SoT)过程为高速模式做准备。表 3 描述了 TX 和 RX 端的事件顺序。

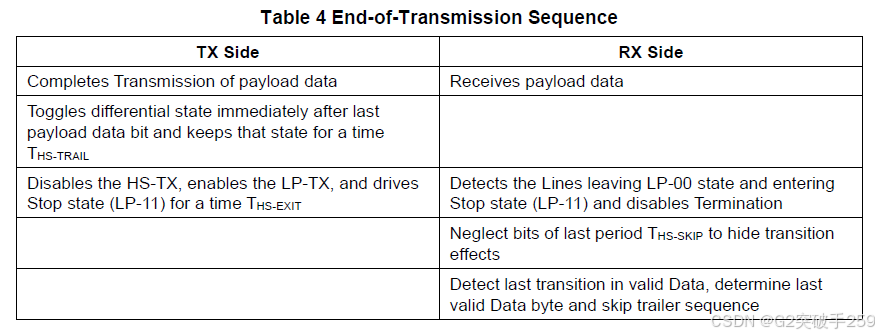

End-of-Transmission

在数据突发结束时,Lane 离开高速传输模式,通过传输结束(EoT)过程进入停止状态。表 4 显示了 EoT 过程中可能的事件序列。EoT 处理可以由协议层或 D-PHY 执行。

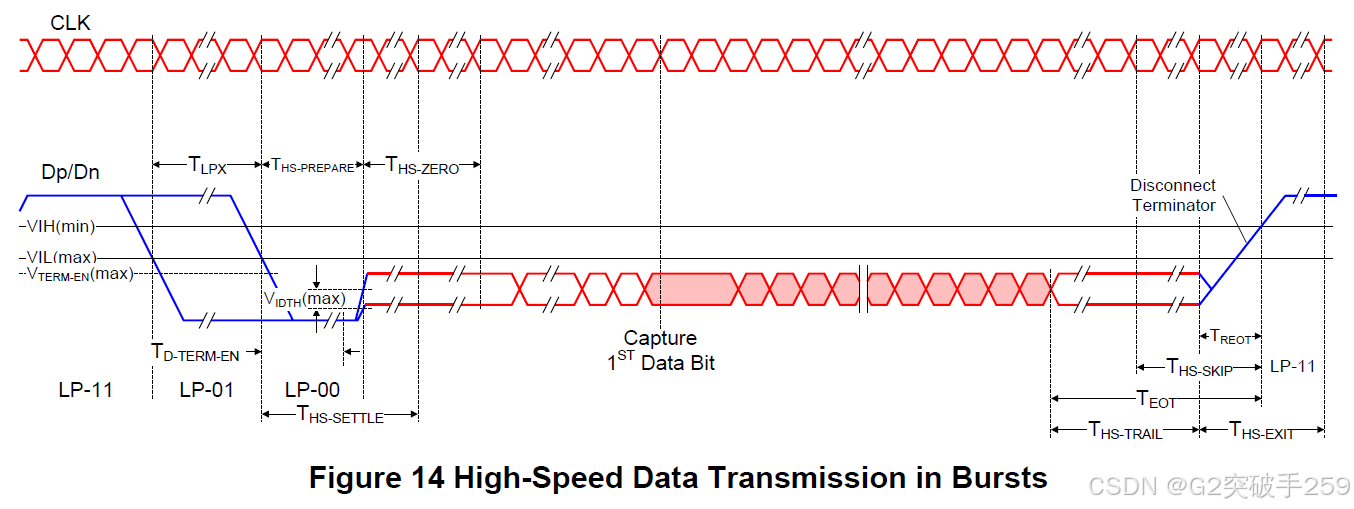

HS Data Transmission Burst

图 14 显示了数据突发传输过程中的事件序列。根据协议,任何 Lane 都可以独立地开始和结束传输。然而,对于大多数应用程序,Lane 将同步启动,但可能在不同的时间结束,因为每个 Lane 传输的字节量不相等。与协议层的握手在附件 A 中描述。

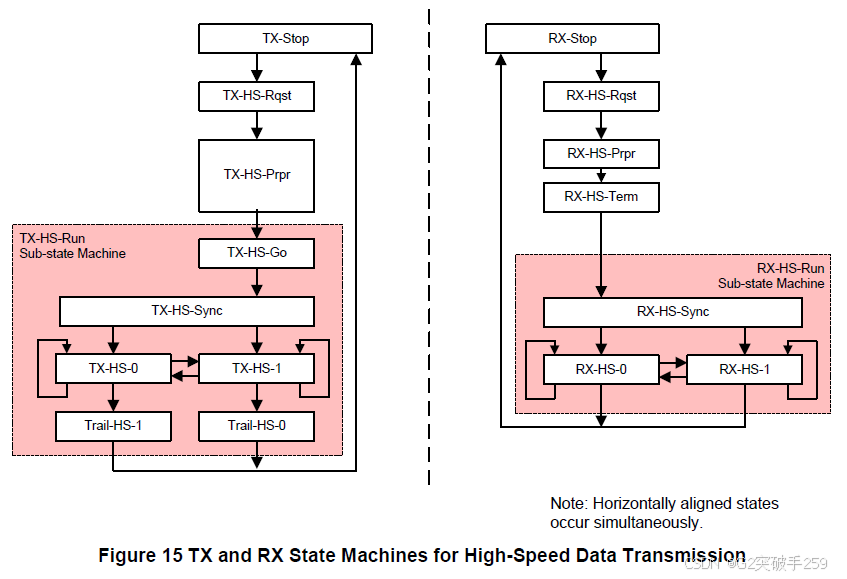

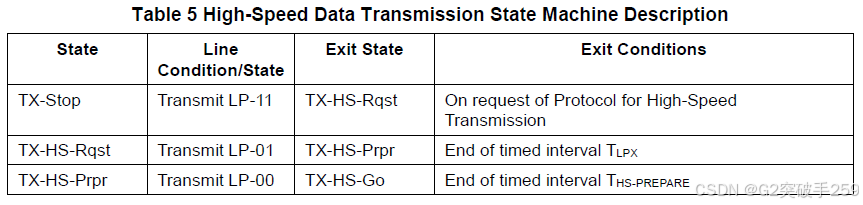

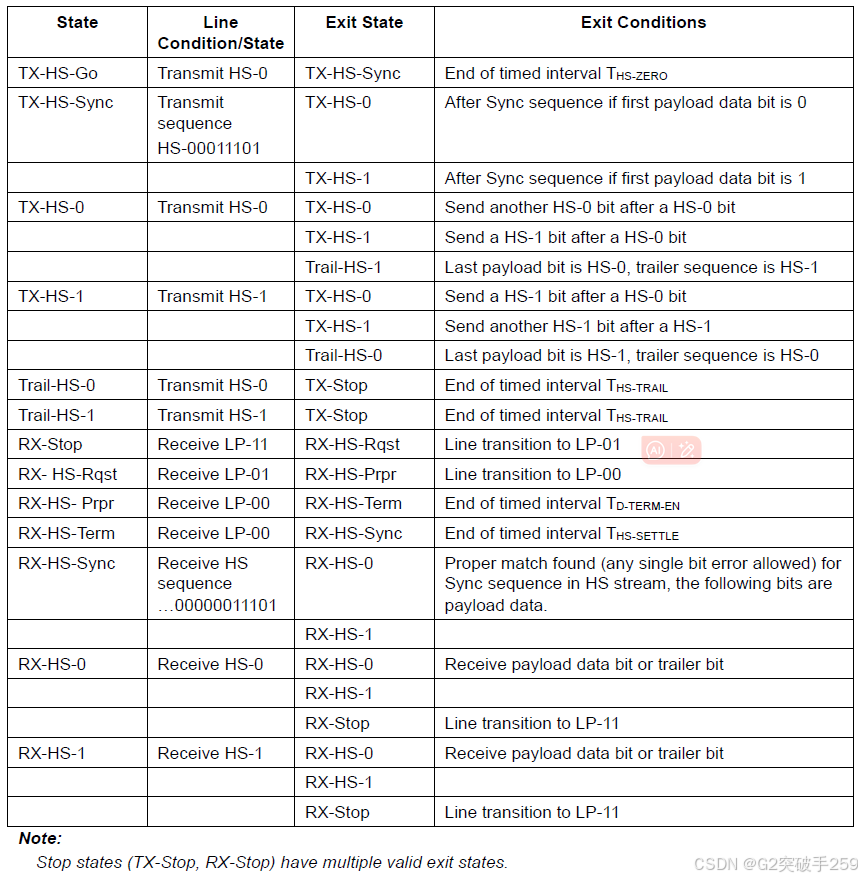

图 15 显示了高速数据传输的状态机,如表 5 所示。

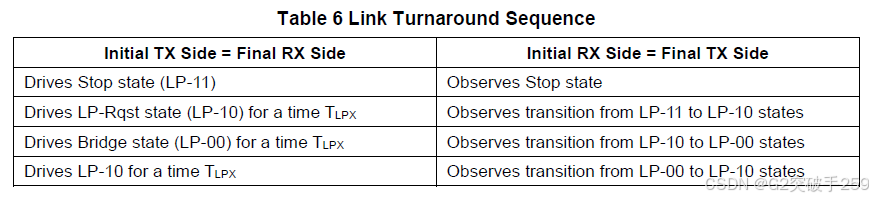

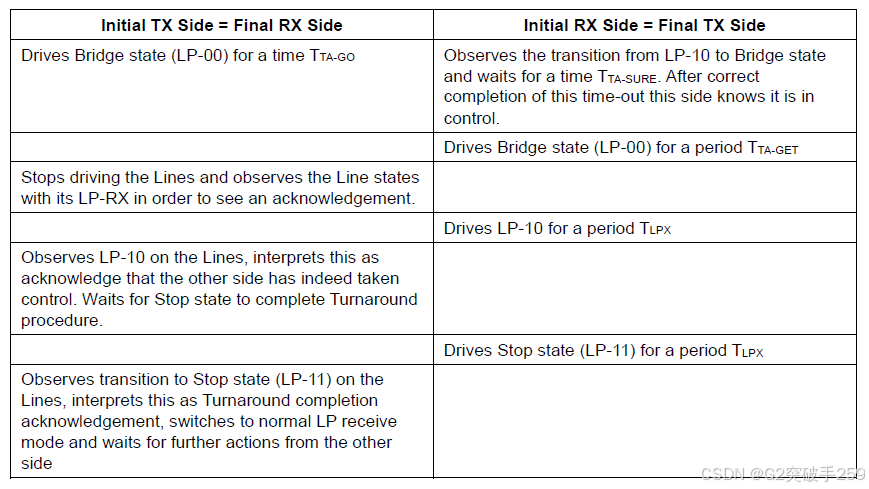

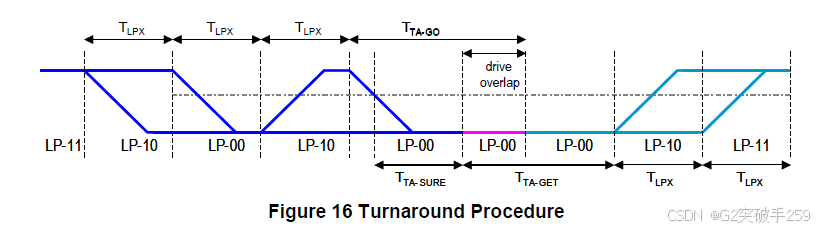

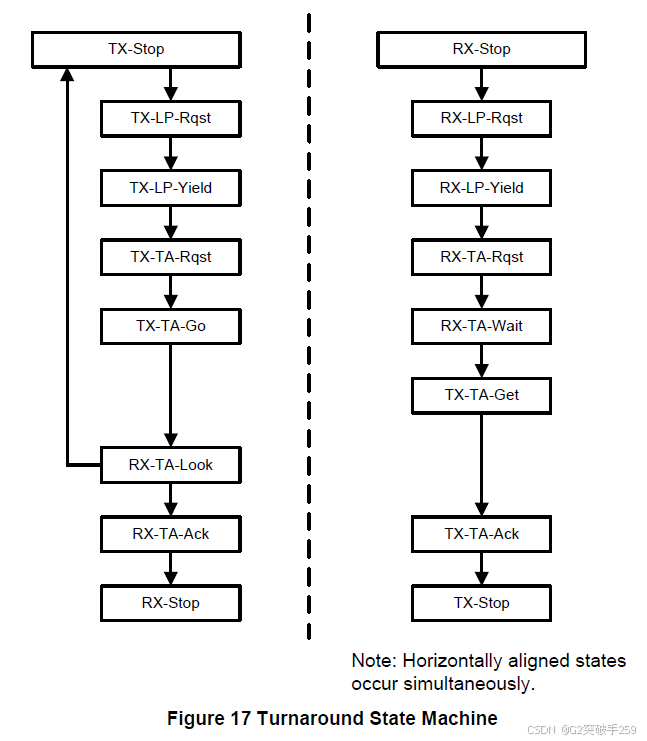

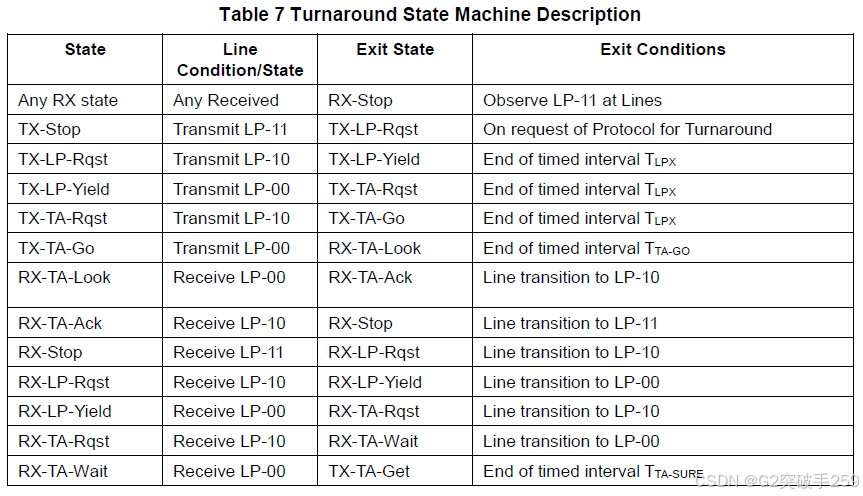

Bi-Directional Lane Turnaround

双向数据通道的传输方向可以通过链路转换过程进行交换。此过程允许在与当前方向相反的方向上传输信息。从正向到反向或从反向到正向的更改过程相同。请注意,主从端不能在转向时更改。链路转向应完全在控制模式下处理。表 6 列出了转向期间的事件顺序。

图 16 以图形方式显示了转向过程。

链路两端的低功耗时钟时序不必相同,但可以不同。然而,低功耗状态周期(tLPX)之间的比率是受限的,以确保适当的转向行为。tLPX(MASTER)与 tLPX(SLAVE)的比值见表 14。

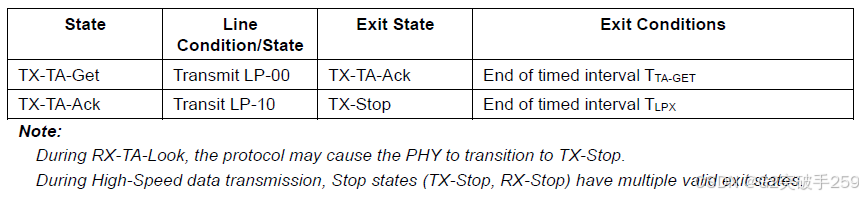

如果通道尚未通过驱动停止状态而进入 TX-LP-Yield 状态,则转向过程可以被中断。驱动停止状态将中止转向过程并使通道返回到停止状态。PHY 应确保在 TX-TA-Rqst、RX-TA-Rqst 或 TX-TA-GO 结束后不中断该过程。一旦 PHY 驱动 TX-LP-Yield,它不应中止转向过程。如果协议层确定由于转向过程没有在一定时间内完成而发生了错误,则可以采取适当的行动。参见第 7.3.5 节了解更多细节。图 17 显示了转向状态机,如表 7 所示。

Escape Mode

Escape 模式是低功耗状态下数据通道的一种特殊操作模式。有了这种模式,一些额外的功能就可用了。在正方向上应支持 Escape 模式操作,在反方向上可选。如果支持,Escape 模式不必包括所有可用的功能。

Lane 应通过 Escape 模式进入程序(LP-11、LP-10、LP-00、LP-01、LP-00)进入 Escape 模式。一旦在线路上观察到最终的桥状态(LP-00),通道将在空间状态(LP-00)下进入 Escape 模式。如果在最终桥接状态(LP-00)之前的任何时间检测到 LP-11,则退出模式进入过程将被中止,接收方将等待或返回到停止状态。

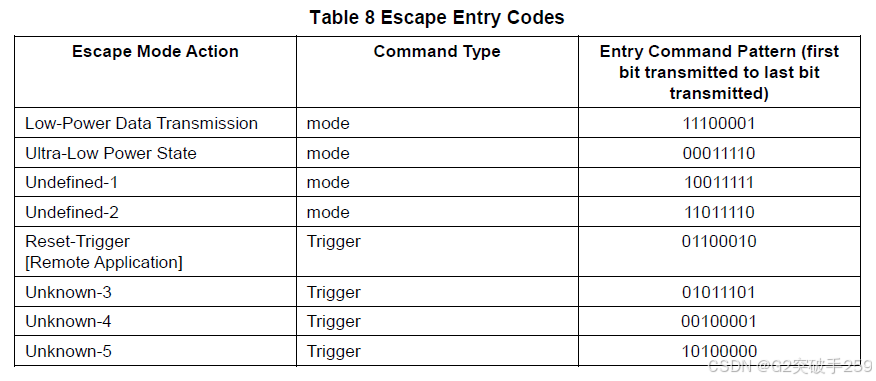

一旦进入 Escape 模式,发送器将发送一个 8-bit 的进入命令来指示请求的操作。表 8 列出了当前所有可用的Escape 模式命令和操作。保留所有未分配的命令以供将来扩展。

停止状态应使用用于退出 Escape 模式,并且由于 spaced-one-hot 编码,在 Escape 模式操作期间不能发生。停止状态立即将通道返回到控制模式。如果输入命令与支持的命令不匹配,则忽略特定的 Escape 模式动作,接收端等待,直到发送端返回到停止状态。

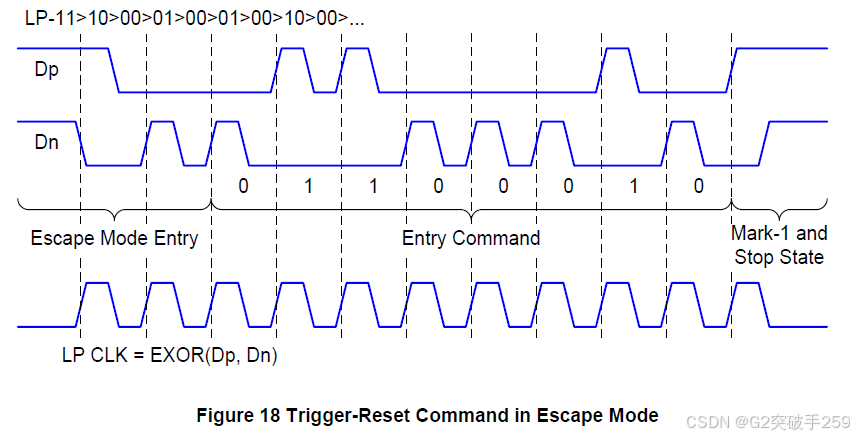

Escape 模式下的 PHY 应采用 spaced-one-hot 编码进行异步通信。因此,在这种模式下,Lane 的操作不依赖于单独的时钟信号。Trigger-Reset 命令的完整 Escape 模式操作如图 18 所示。

spaced-one-hot 编码意味着每个 Mark 状态与一个 Space 状态交织在一起。因此,每个符号由两个部分组成:一个 one-hot 相位(Mark-0 or Mark-1)和一个 space 相位。TX 发送 Mark-0 后加 Space 来发送一个 “零比特”,发送 Mark-1 后加 Space 来发送一个 “一比特”。Mark 后面没有 Space 就不代表一个位。在退出具有停止状态的 Escape 模式之前的最后一个阶段应该是 Mark-1 状态,它不是通信位的一部分,因为它后面没有 Space 状态。时钟可以通过异或函数从 Dp 和 Dn 两条线信号中得到。每个 LP 状态周期的长度至少为 tLPX,MIN。

Remote Triggers

触发信号是一种根据发送端的协议层的请求,向接收端的协议层发送标志的机制。这既可以在前进方向,也可以在反向方向,这取决于操作方向和可用的 Escape 模式功能。触发信号要求具有 Escape 模式功能,并且在接口的两端至少有一个匹配的 Trigger Escape Entry 命令。

图 18 显示了一个 Escape Mode Reset-Trigger 操作的示例。Lane 通过 Escape 模式进入程序进入 Escape 模式。如果输入命令模式与 Reset-Trigger 命令匹配,则通过逻辑 PPI 将 Trigger 标记到接收端的协议层。在触发命令之后但在行进入停止状态之前收到的任何位都将被忽略。因此,可以将虚拟字节连接起来,以便向接收端提供时钟信息。

请注意,包括 Reset-Trigger 在内的 Trigger 信号是一个通用的消息传递系统。触发器命令不影响 PHY 本身的行为。因此,协议层可以将触发器用于任何目的。

Low-Power Data Transmission

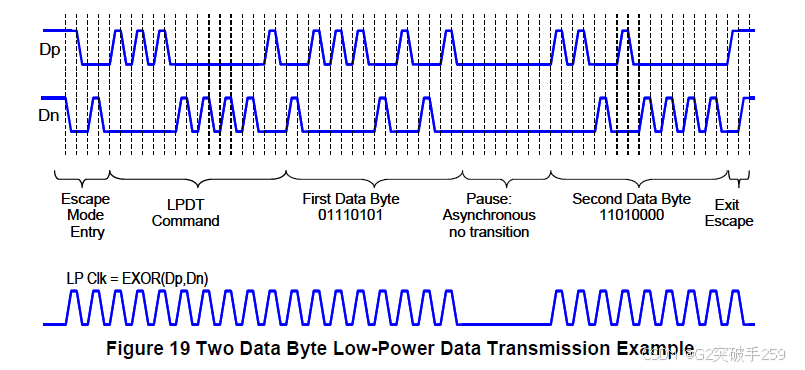

如果在 Escape 模式进入过程之后加上 LPDT (Low-Power Data Transmission)进入命令,则协议层可以低速传输数据,而 Lane 保持在低功耗模式。

数据应在行上使用与输入命令相同的 spaced-one-hot 编码。数据由应用的位编码生成时钟,不依赖于时钟通道。Lane 可以在使用 LPDT 时暂停,方法是在行上保持一个 Space 状态。线路上的 Stop 状态停止 LPDT,退出 Escape 模式,并将 Lane 切换到控制模式。停止状态之前的最后一个阶段应该是 Mark-1 状态,它不代表一个数据位。图 19 显示了一个两字节的传输,两个字节之间有一个暂停期。

使用 LPDT,提供给发送端的低功率(位)时钟信号(fMOMENTARY < 20MHz)用于传输数据。数据接收由位编码生成时钟。因此,可以允许可变时钟速率。在 LPDT 结束时,通道应返回到停止状态。

Ultra-Low Power State

如果在 Escape 模式进入命令后发送超低功耗状态进入命令,则 Lane 将进入超低功耗状态(ULPS)。该命令将被标记为接收端协议。在此状态下,行处于 Space 状态(LP-00)。超低功耗状态通过一个长度为 tWAKEUP 的 Mark-1 状态退出,随后是一个停止状态。附件 A 描述了一个退出过程的示例和一个控制在 Mark-1 状态中花费的时间长度的过程。

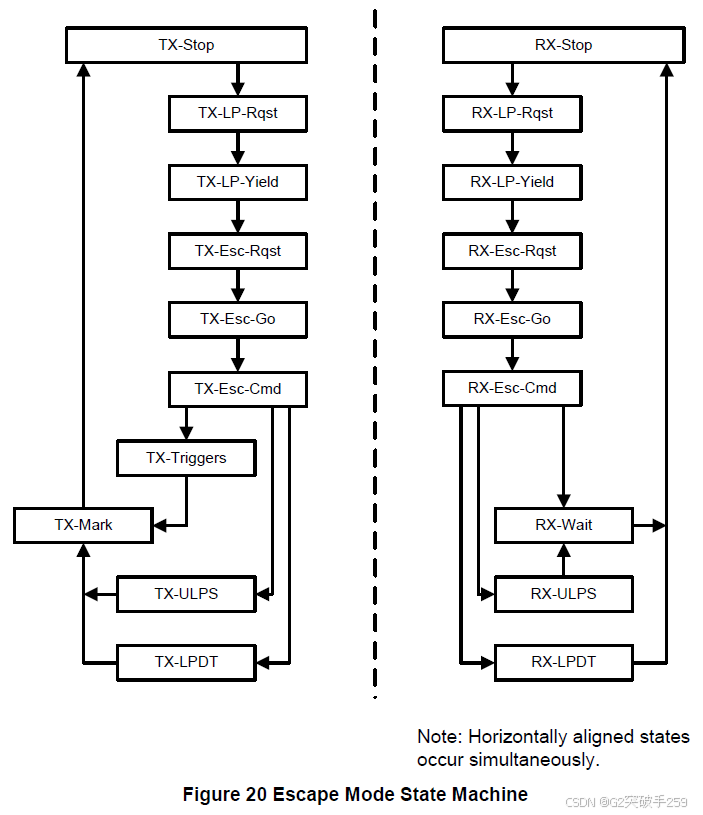

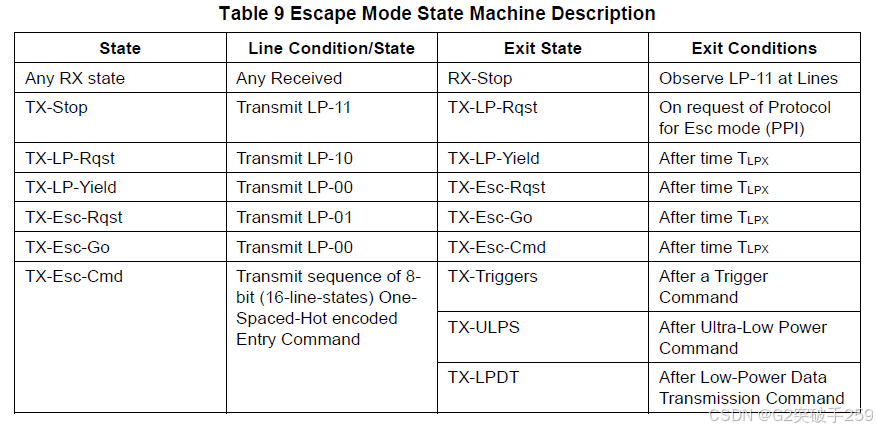

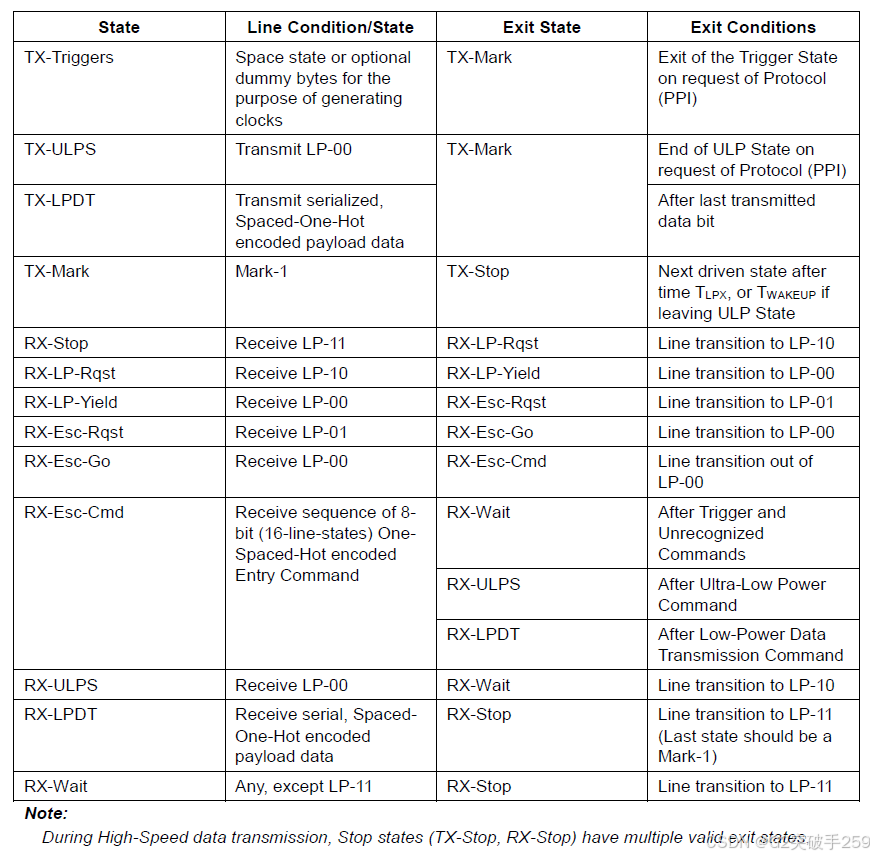

Escape Mode State Machine

Escape 模式操作的状态机如图 20 所示,如表 9 所示。

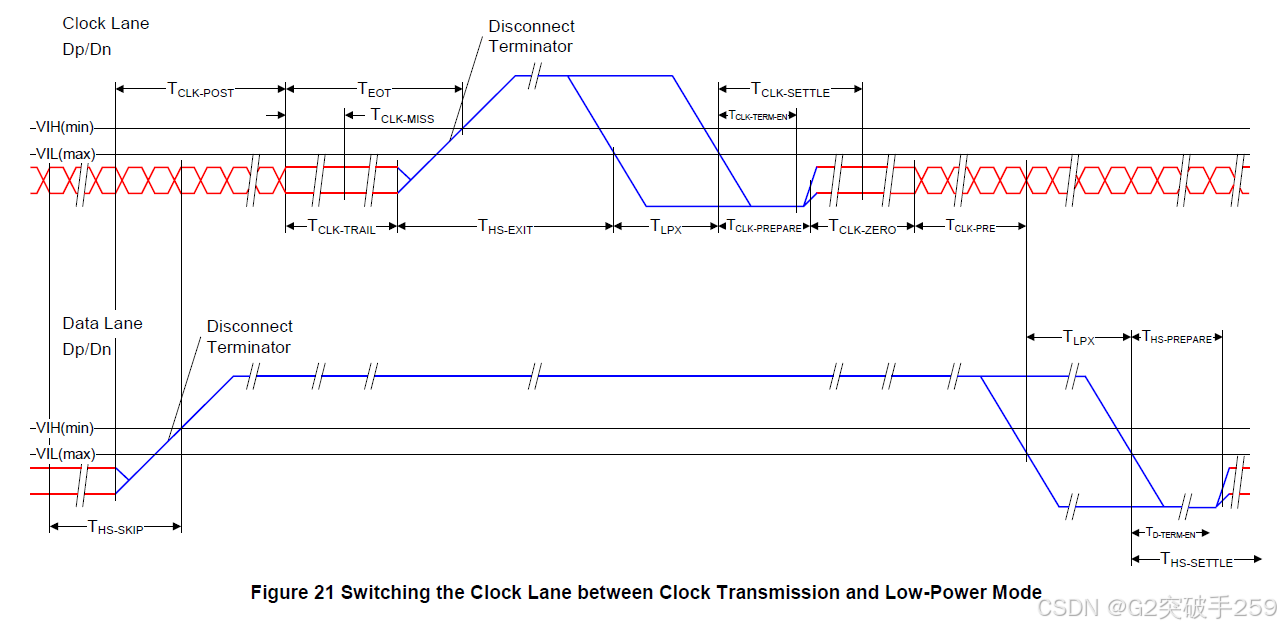

High-Speed Clock Transmission

在高速模式下,时钟通道为高速数据传输提供从主到从的低摆幅差分 DDR 时钟信号。时钟信号应具有相对于向前方向的数据通道上的切换位序列的正交相位,并且在突发的第一个传输位的中心具有上升沿。数据 - 时钟关系和时序规范的细节可以在第 10 节中找到。

时钟通道类似于单向数据通道。然而,存在一些时序差异,时钟通道传输高速 DDR 时钟信号而不是数据位。此外,时钟通道和数据通道的低功耗模式功能定义不同。时钟通道应该是单向的,不包括常规的 Escape 模式功能。只有 ULPS 应该通过使用 LP-Request 状态的特殊入口序列来支持。高速时钟传输应从停止状态开始,并退出到停止状态。

时钟通道模块由协议通过时钟通道 PPI 控制。只有当任何数据通道中没有高速传输活动时,协议才应停止时钟通道。

时钟通道设置为 “低功耗” 模式,会延长数据通道的 “高速数据传输” 启动时间。在这种情况下,时钟通道应首先恢复到高速运行,然后才能处理发送请求。

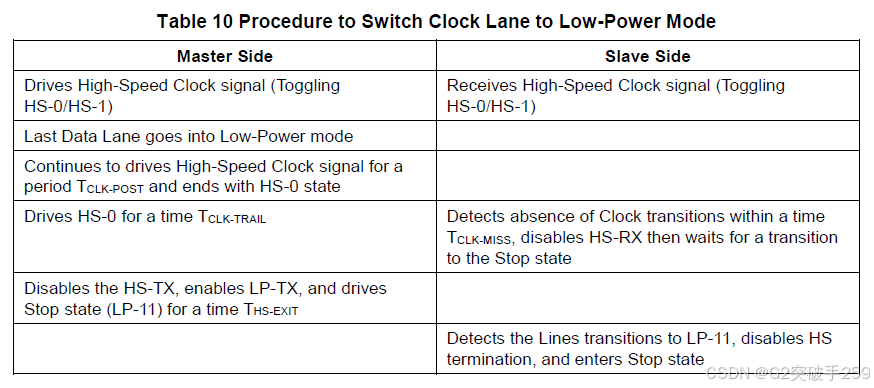

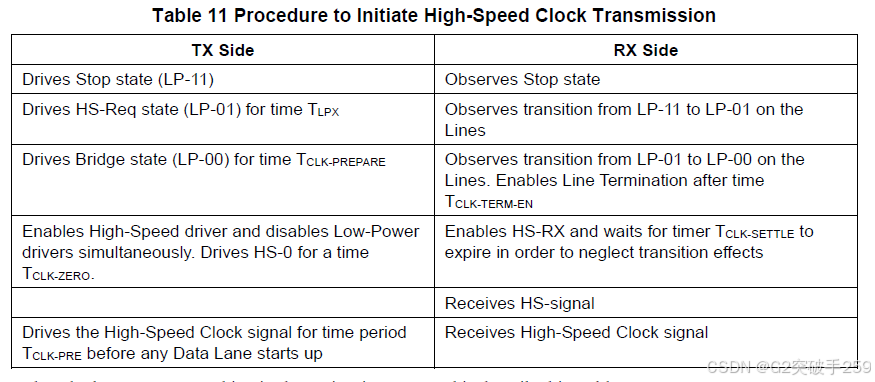

高速时钟信号应在最后一个数据通道切换到低功耗模式并以 HS-0 状态结束后继续运行一段时间 TCLK-POST。表 10 给出了时钟通道切换到低功耗模式的过程。请注意,时钟突发总是包含偶数转换,因为它开始和结束 HS-0 状态。这意味着时钟提供了在任何相关数据通道上采样偶数位的转换。时钟周期应可靠,并符合 HS 时序规范。表 11 给出了将时钟通道返回到高速时钟传输的过程。Clock Start 和 Stop 过程如图 21 所示。

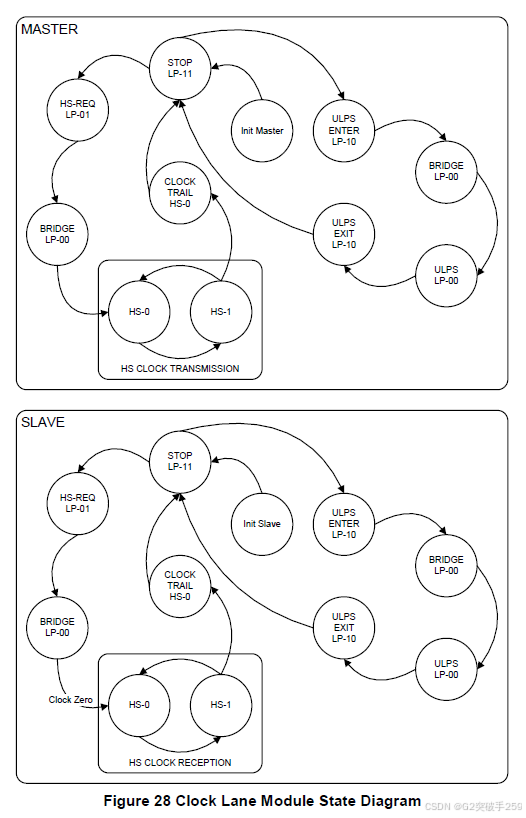

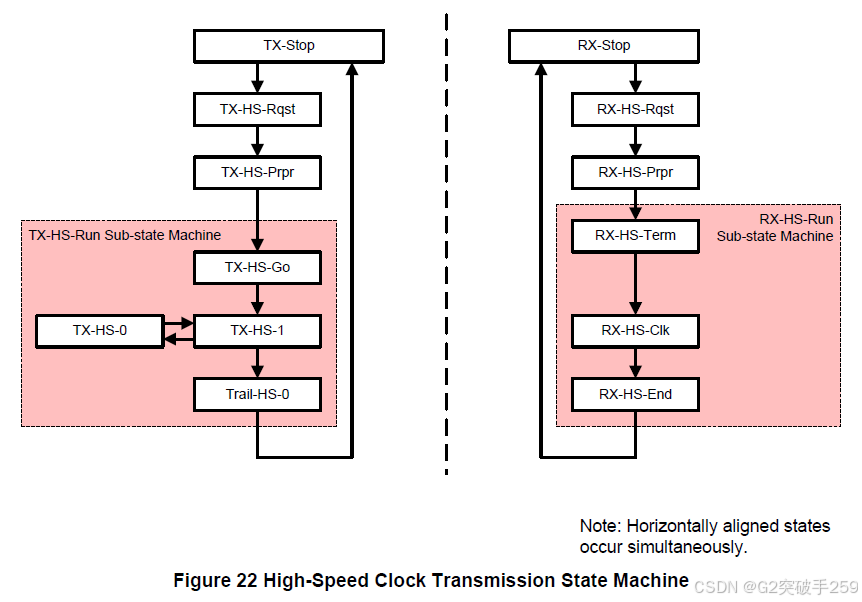

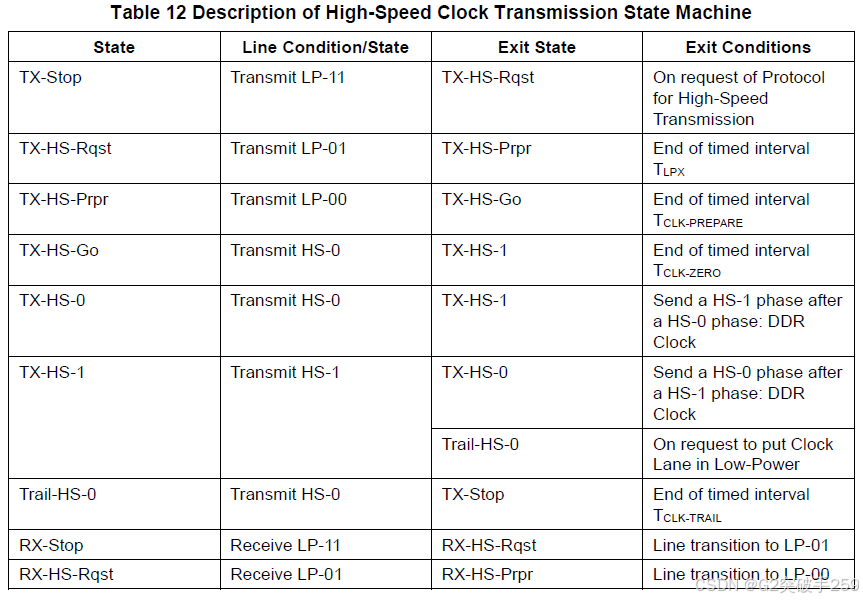

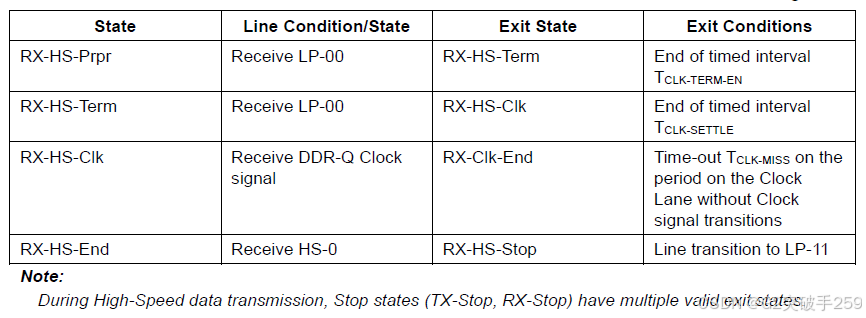

时钟通道状态机如图 22 所示,如表 12 所示。

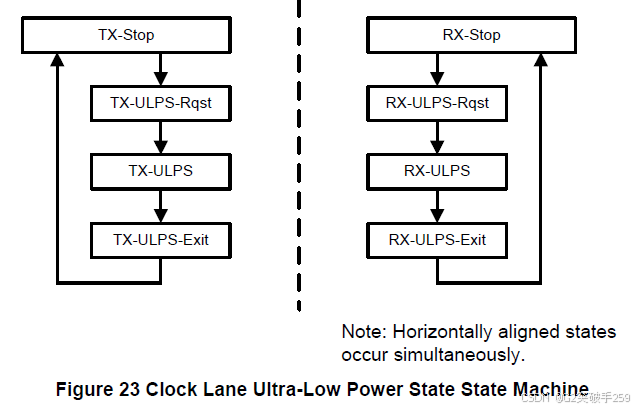

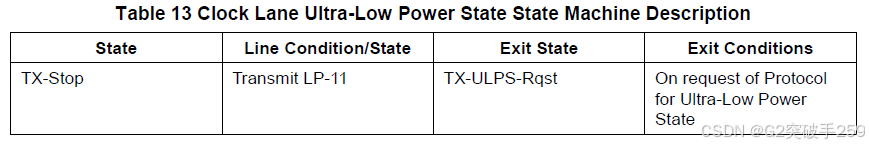

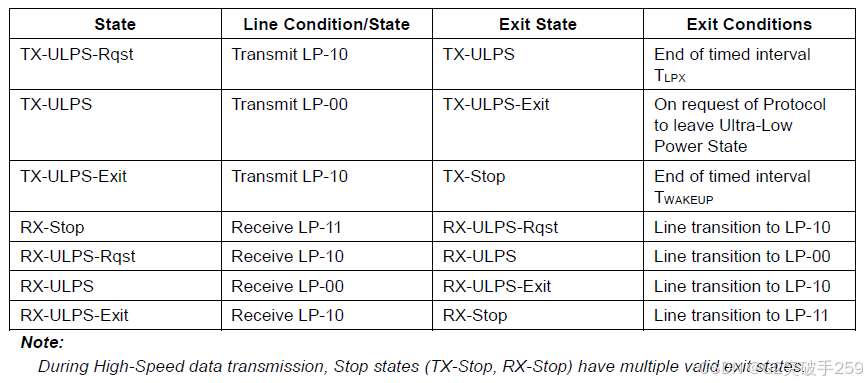

Clock Lane Ultra-Low Power State

虽然时钟通道不包括常规的 Escape 模式,但时钟通道应支持超低功耗状态。

时钟通道应通过时钟通道超低功耗状态进入程序进入超低功耗状态。在这个过程中,发送端从 Stop 状态开始驱动 TX-ULPS-Rqst State (LP-10),然后驱动 TX-ULPS State (LP-00)。在此之后,时钟通道将进入超低功耗状态。如果发生错误,并且在 TX-ULPS-Rqst State 之后立即检测到 LP-01 或 LP-11,则终止超低功耗状态进入过程,接收端分别等待或返回到 Stop 状态。

接收端 PHY 应将 ULP 状态的出现标记给到接收端协议。在此状态下,线路处于 ULP 状态(LP-00)。超低功耗状态通过长度为 TWAKEUP 的 Mark-1 TX-ULPS-Exit 状态退出,然后是停止状态。附录 A 描述了一个退出程序的示例,该程序允许控制在 Mark-1 TX-ULPS-Exit 状态中花费的时间长度。

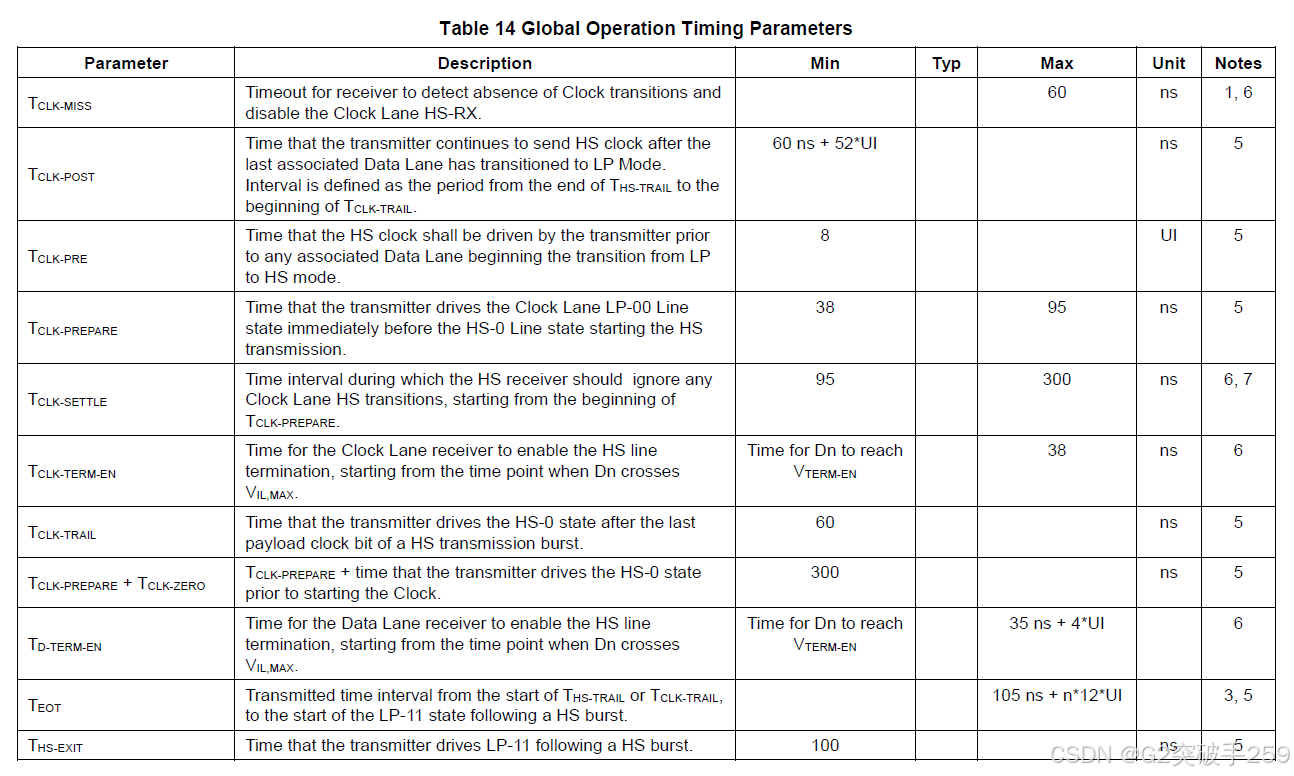

Global Operation Timing Parameters

表 14 列出了本节中使用的所有定时参数的范围。表中的值假设 UI 在 △UI 定义的范围内发生变化(见表 29)。

发送器应支持表 14 中定义的所有发送器特有的定时参数。

接收器应支持表 14中 定义的所有特定于接收器的定时参数。

还要注意的是,虽然没有为每个发送器特定参数定义相应的接收器公差,但接收器还应支持接收表 14 中所有发射机特定时序参数的所有允许的一致性值,所有 HS UI 值直至并包括接收器数据表中指定的最大支持 HS 时钟速率。

Global Operation Flow Diagram

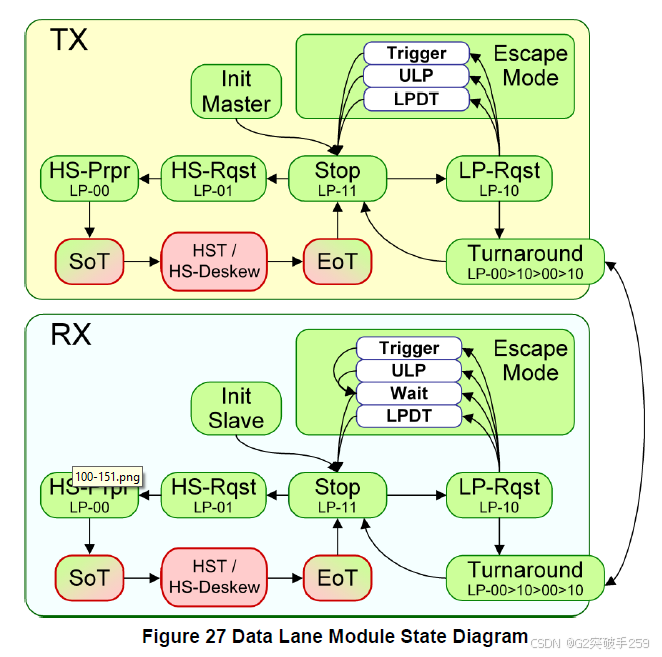

所有先前描述的操作方面,包括或不包括可选部件,都包含在 Lane 模块中。图 27 显示了数据通道模块的操作流程图。在 TX 和 RX 中,可以区分出四个主要进程:高速传输、Escape 模式、转向和初始化。

图 28 显示了时钟通道模块的状态图。时钟通道模块有四种主要的运行状态:初始化(持续时间不确定)、低功耗停止状态、超低功耗状态和高速时钟传输。该图还显示了前面描述的转向状态。