文章目录

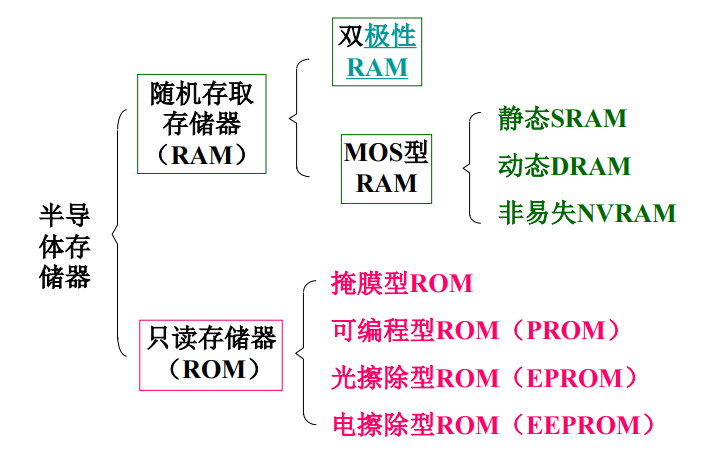

- 半导体存储器的分类及特点(了解即可)

- 半导体存储器的性能指标

- 半导体存储器芯片与CPU的连接

- 存储器与CPU之间的时序配合(了解即可)

- 存储芯片的组成

- Flash闪存(了解即可)

- Cache高速缓存

- 半导体存储器的寻址方法及其应用

- 片选

- 线选法

- 译码法

- 部分译码法

- 全译码法

- 字选

- 全地址译码

- 部分地址译码

- 读写控制

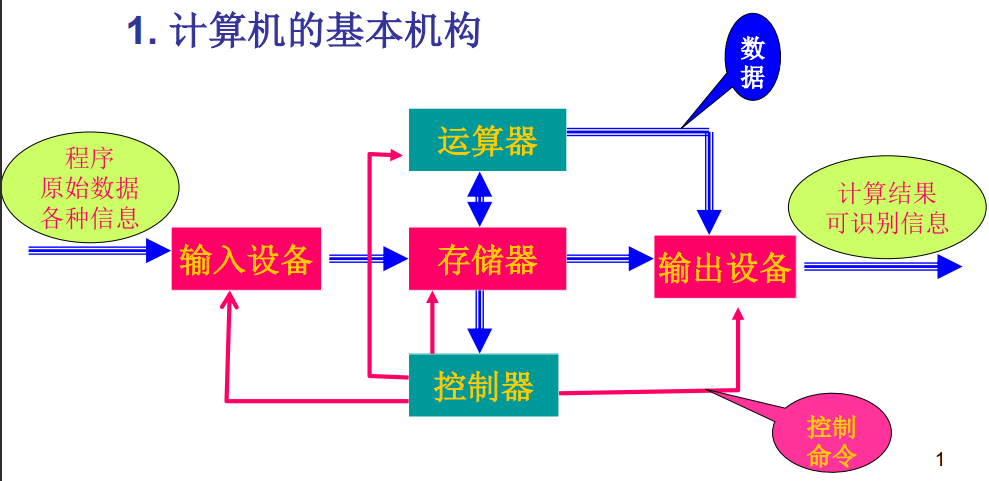

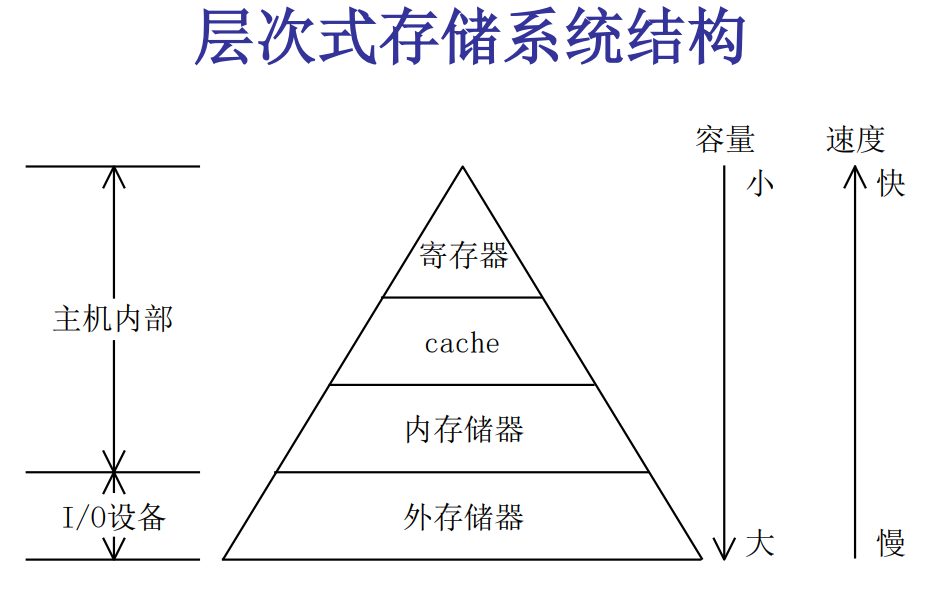

两大类存储器:

- 内存——存放当前运行的程序和数据,又称为主存储器

- 特点:存取速度快,容量小,功耗低,集成度高,随机存取,CPU可直接访问。

- 通常由半导体存储器构成

- RAM、ROM

- 外存——存放非当前使用的程序和数据。

- 特点:存取速度慢,容量大,顺序存取/块存取。需调入内存后CPU才能访问。

- 通常由磁、光存储器构成,也可以由半导体存储器构成

- 磁盘、磁带、CD-ROM、DVD-ROM、固态盘

半导体存储器的分类及特点(了解即可)

- 按制造工艺

- 双极型:速度快、集成度低、功耗大

- 单极MOS型:速度慢、集成度高、功耗低

- 按使用属性

- 随机存取存储器RAM:可读可写、断电丢失

- 只读存储器ROM:正常只读、断电不丢失

这个图知道就行了

半导体存储器的性能指标

- 存储器容量:一个存储器芯片上能存储多少个用二进制表示的信息位数。

- 存取时间:指向存储器单元写入数据及从存储器单元读出数据所需的时间(ns)。

- 功耗

- 工作电源:TTL供电电压+5V,MOS供电电压+3V ~ +18V

- DRAM的刷新:因为数据存在电容上,所以总需要刷新来维持电容上的电荷,以保持信息。(一般为2ms)

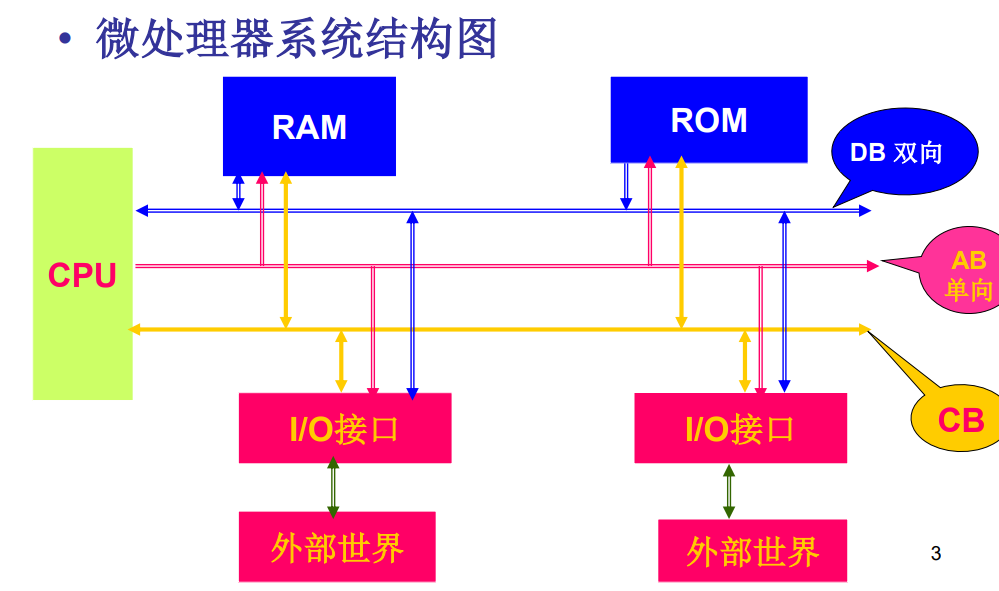

半导体存储器芯片与CPU的连接

存储器与CPU之间的时序配合(了解即可)

• 选用存储芯片时,必须考虑它的存取速度和CPU速度的匹配问题,即时序配合。

• 为了使CPU能与不同速度的存储器相连接,一种常用的方法是使用“等待申请”信号。该方法是在CPU设计时设置一条“等待申请”输入线。

• 若与CPU连接的存储器速度较慢,使CPU在规定的读/写周期内不能完成读/写操作,则在CPU执行访问存储器指令时,由等待信号发生器向CPU发出“等待申请”信号,使CPU在正常的读/写周期之外再插入一个或几个等待周期Tw,以便通过改变指令的时钟周期数使系统速度变慢,从而达到与慢速存储器匹配的目的。

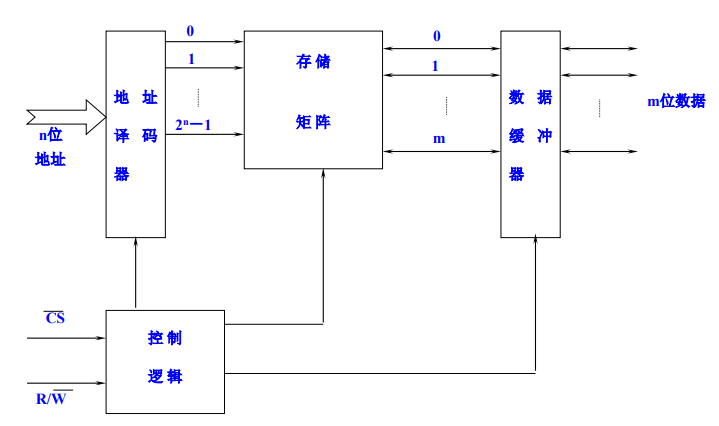

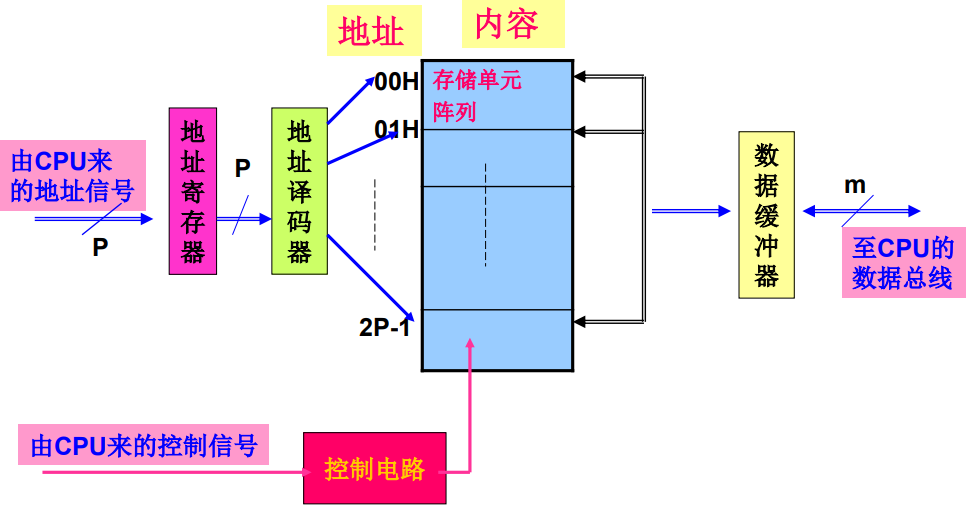

存储芯片的组成

- 存储单元地址:每个存储单元有一个地址

- 存储体内基本存储元的排列结构通常有两种。 一种是“多字一位”结构(简称位结构),其容量表示成N字×1位。例如,1K×1位,4K×1位。另一种排列是“多字多位”结构(简称字结构),其容量表示为:N字×4位/字或N字×8位/字。如静态RAM的6116为2K×8,6264为8K×8等。

- 地址译码器:接收来自CPU的N位地址,经译码后产生2n个地址选择信号

- 控制逻辑电路:接收片选信号及来自CPU的读/写控制信号,形成芯片内部控制信号

- 数据缓冲器:用于暂时存放来自CPU的写入数据或从存储体内读出的数据。

M*N的表示方法,M是存储单元数,N是每个存储单元由多少位

芯片内部结构就像这样(了解即可)

Flash闪存(了解即可)

快速擦写存储器(Flash Memory)也称为闪速存储器

- 按区块(Sector)或页面(Page)组织

可进行整个芯片的擦除和编程操作外,还可以进行字节、区块或页面的擦除和编程操作 - 可进行快速页面写入

CPU可以将页数据按芯片存取速度(一般为几十到200ns)写入页缓存,再在内部逻辑的控制下,将整页数据写入相应页面,大大加快了编程速度。

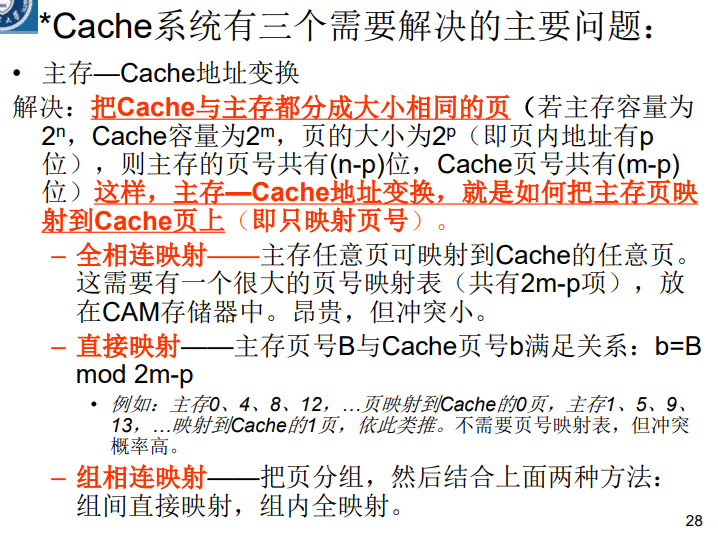

Cache高速缓存

为什么需要高速缓存?

- CPU工作速度与内存工作速度不匹配

- 在CPU和RAM之间插入高速缓存——成本上升不多、但速度可大幅度提高。

工作原理:

- 基于程序执行的两个特征:

- 程序访问的局部性:过程、循环、子程序。

- 数据存取的局部性:数据相对集中存储。

- 正确的术语应该叫时间局部性(temporal locality)和空间局部性(sequential locality)

- 存储器的访问相对集中的特点使得我们可以把频繁访问的指令、数据存放在速度非常高(与CPU速度相当)的SRAM——高速缓存CACHE中。需要时就可以快速地取出。

工作方式:

- 取指令、数据时先到CACHE中查找:

- 找到(称为命中)——直接取出使用;

- 没找到——到RAM中取,并同时存放到CACHE中,以备下次使用。

- 只要命中率相当高,就可以大大提高CPU的运行效率,减少等待。现代计算机中CACHE的命中率都在90%以上。

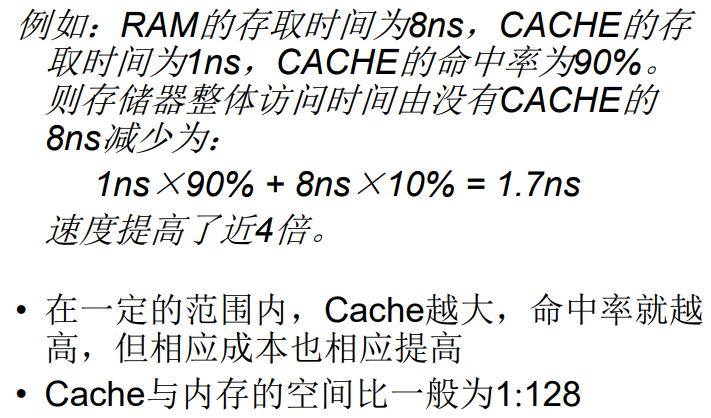

- 命中率影响系统的平均存取速度系统的

平均存取速度≈Cache存取速度×命中率+RAM存取速度×不命中率

(了解即可)

• 不命中时如何替换Cache内容

有以下几种替换算法:

– 随机替换

– 先进先出FIFO

– 最近最少使用LRU(Least Recently Used)

– 最久没有使用LFU(Least Frequently Used)

• Cache与主存的一致性(了解即可)

两种常用的更新算法:

– 写穿式(WT,Write Through)——同时更新

– 回写式(WB,Write Back)——仅当替换时才更新主存

Cache读写操作(了解即可)

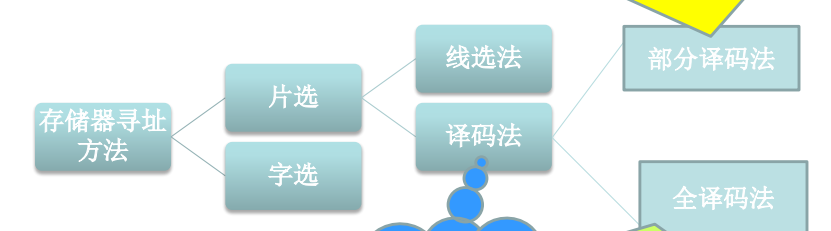

半导体存储器的寻址方法及其应用

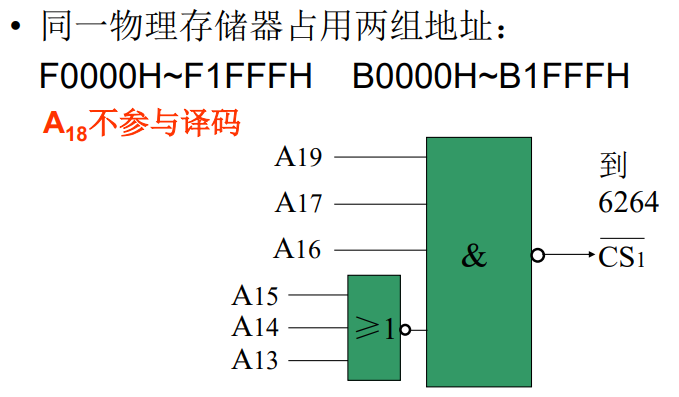

部分译码:

片选地址线中仅有一部分参加译码,可保证存储器芯片的地址连续,但一个存储单元会对应多个地址,及地址重叠。若有n条片选地址线未参加译码,则存储单元的重叠地址为2的n次幂个

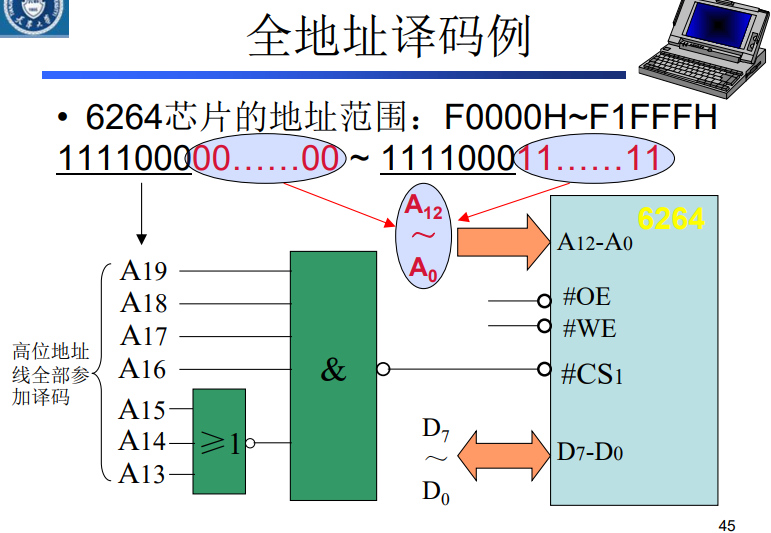

全译码:

电路控制存储器芯片的片选端片选地址线中仅有一部分参加译码,可保证存储器芯片的地址连续,但一个存储单元会对应多个地址,及地址重叠。若有n条片选地址线未参加译码,则存储单元的重叠地址为2的n次幂个片选地址线全部参加译码。保证每个存储单元只有唯一的地址,便于主存储器系统的扩展

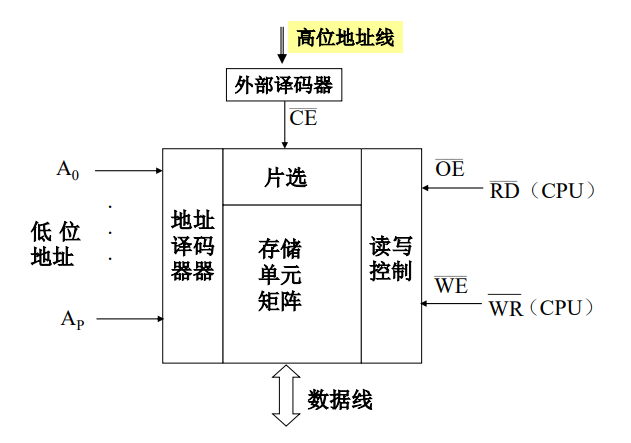

片选

通过地址线,选中某一存储器芯片

所以说:几个存储芯片的地址线一样(低地址),但是使能引脚接不同的地址线(高地址)。(有些芯片没被使能)

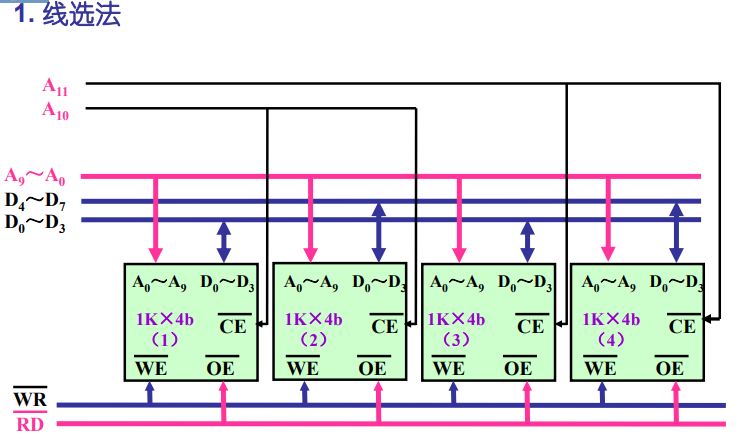

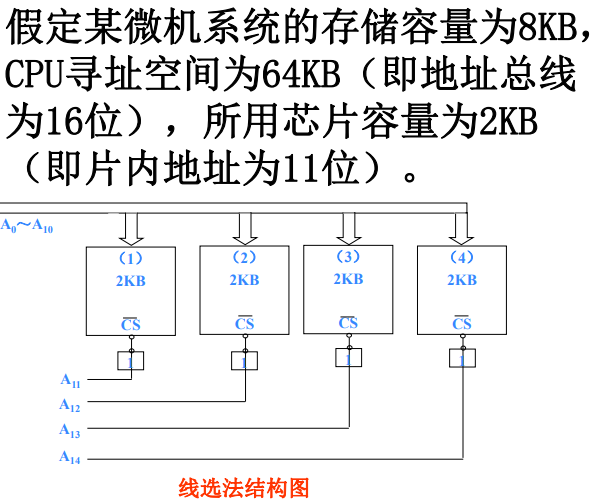

线选法

- 线选法是指高位地址线不经过译码,直接作为存储芯片的片选信号。

- 每根高位地址线接一块芯片的片选,用低位地址线实现片内寻址字选。

- 线选法的优点是结构简单,不需另外的硬件;缺点是地址空间浪费大,地址空间不连续,而且由于部分地址线未参加译码,还会出现地址重叠。

译码法

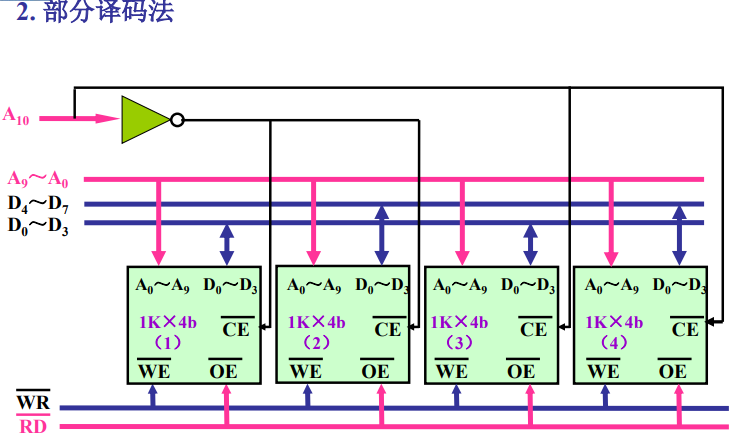

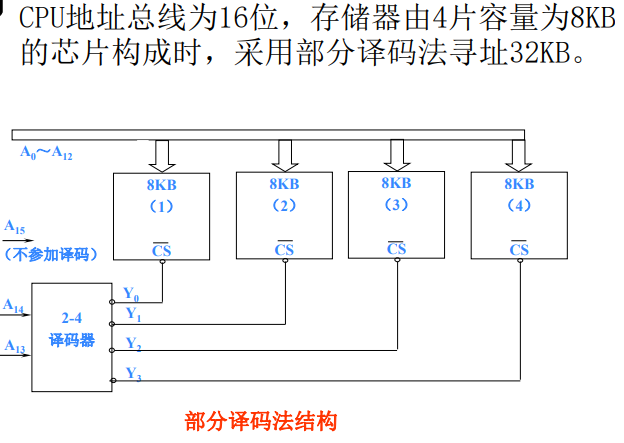

部分译码法

- 部分译码法是将高位地址线中的一部分(而不是全部)进行译码,产生片选信号。

- 采用部分译码法时,由于未参加译码的高位地址与存储器地址无关,因此存在地址重叠问题。

- 该方法常用于不需要全部地址空间的寻址能力,但采用线选法地址线又不够用的情况。

- 当选用不同的高位地址线进行部分译码时,其译码对应的地址空间不同。

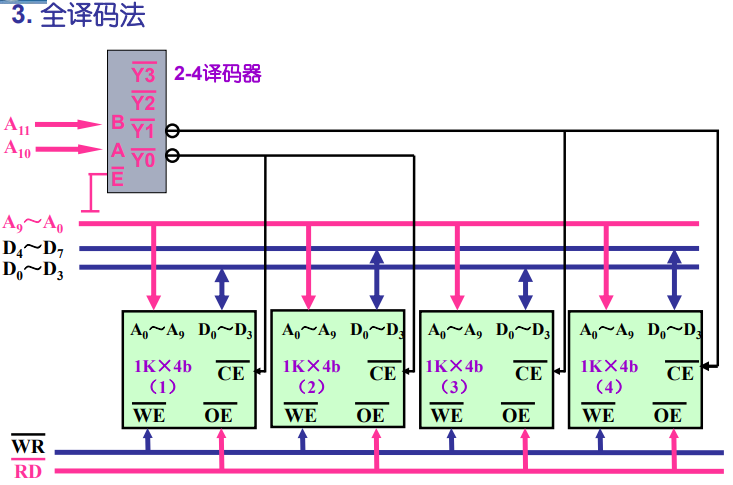

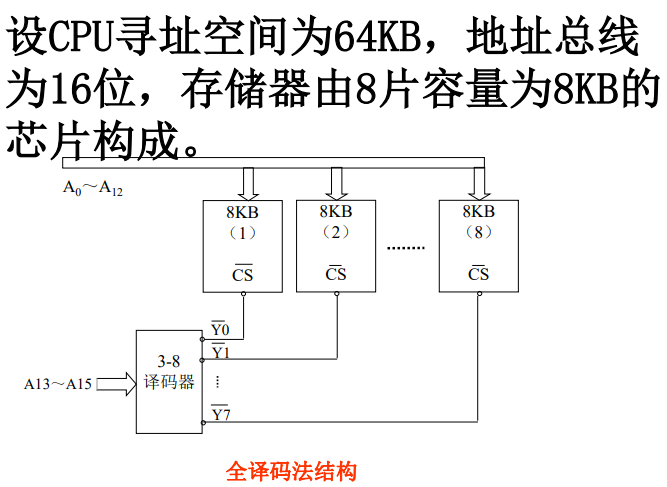

全译码法

- 全译码法是指将地址总线中除片内地址以外的全部高位地址接到译码器的输入端参与译码。

- 采用全译码法,每个存储单元的地址都是唯一的,不存在地址重叠,但译码电路较复杂,连线也较多。

- 全译码法可以提供对全部存储空间的寻址能力。当存储器容量小于可寻址的存储空间时,可从译码器输出线中选出连续的几根作为片选控制,多余的令其空闲,以便需要时扩充。

字选

选中存储器芯片片内存储单元

就是说:所有的存储芯片都被使能,但是数据线不相同???()

全地址译码

通过提前加入逻辑门进行约束,避免了出现地址重叠的问题

部分地址译码

通过将某根线悬空,故意产生重叠地址

- 用部分高位地址信号(而不是全部)作为译码信号,使得被选中得存储器芯片占有几组不同的地址范围。

- 下例使用高5位地址作为译码信号,从而使被选中芯片的每个单元都占有两个地址,即这两个地址都指向同一个单元。

读写控制

存储芯片的读写控制

- 芯片OE与系统的读命令线相连当芯片被选中、且读命令有效时,存储芯片将开放并驱动数据到总线

- 芯片WE与系统的写命令线相连当芯片被选中、且写命令有效时,允许总线数据写入存储芯片