一、说明

GMSL(Gigabit Multimedia Serial Links),中文名称为千兆多媒体串行链路,是Maxim公司(现属于ADI)推出的一种高速串行接口,通过同轴电缆或屏蔽双绞线(STP)传输高速串行数据,用于汽车摄像头和显示器应用。GMSL2就是指ADI专有的第二代千兆多媒体串行链路技术,传输速率最高6Gbps。

GMSL的核心技术为串行器/解串器技术,简称SerDes。首先通过串行器将并行数据流转为串行数据流,然后通过更高的频率进行传输,之后通过解串器将接收到的串行数据流转换为并行数据流。另外需要说明的是,GMSL是双向传输,6Gbps是指正向通道最大速率,反向通道最大速率支持1.5Gbps。其主要竞争对手的TI的FPD Link。

本文主要基于GMSL2 Hardware Design and Validation Guide Revision 1.1,介绍GMSL2的原理图设计和PCB布板要求。

二、原理图设计要求

1.原理图的checklist

SCH原理图设计推荐按检查以下内容:

-

所有电源引脚都使用推荐的符合要求耐压容差的去耦电容;

-

单端链路在(-)引脚上具有适当的端接;

-

选择正确的AC耦合电容;

-

I2C/UART线路上使用尺寸适当的上拉电阻;

-

通用输出管脚GPO采样开漏输出,使用时务必接上拉电阻;

-

晶振/晶体正确连接;

-

XRES管脚接一个公差1%的402Ω电阻;

-

CFG管脚连接正确的分压电阻;

-

输入/输出视频接口正确连接;

-

RGMII, SPI, 和I2S要正确连接;

-

确认实际应用必须的AECQ等级;

-

使用推荐的POC电路或已验证新的POC线路;

-

POC最大最小电压满足系统要求;

2.AC耦合电容和端接

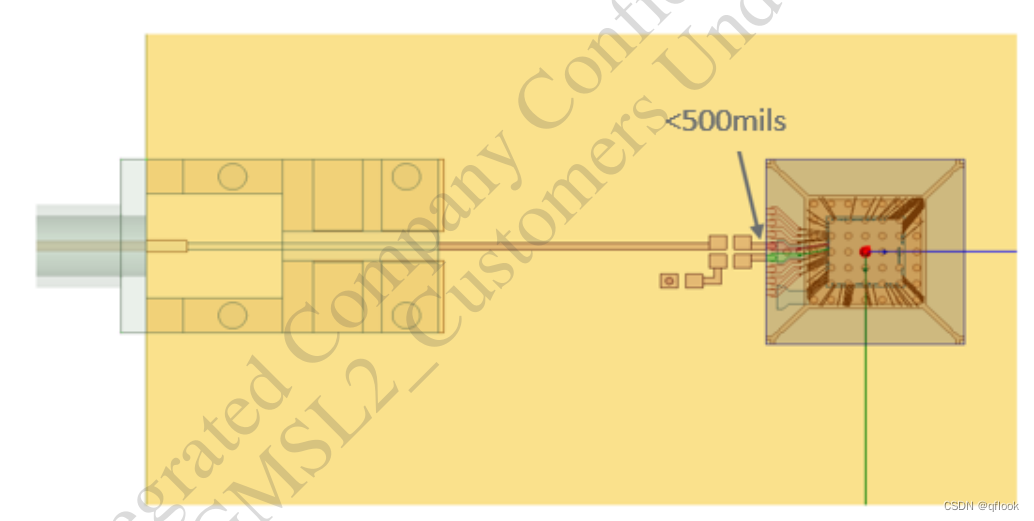

为防止反射,AC耦合电容应尽量靠近芯片,具体要求是距离不超过1/2*UI长度,例如6Gbps要求小于500mil(一般PCB每ns传输15cm,一个UI则传输2.5cm≈1000mil,一半就是500mil);

同轴电缆模式:

-

positive (+)一般用来传输数据(具体参考规格书,部分芯片明确要求要用-管脚);

-

选择合适大小的电容(参考表1);

-

Negative (-)应该使用1个100nF电容+1个50Ω电阻端接到GND;

-

推荐使用0402的电容,更大的电容器会导致阻抗失配,从而降低性能(实测0201的电容S参数更好,但价格更贵);

-

电容的额定电压超过POC最大电压,防止长时间老化的退化;

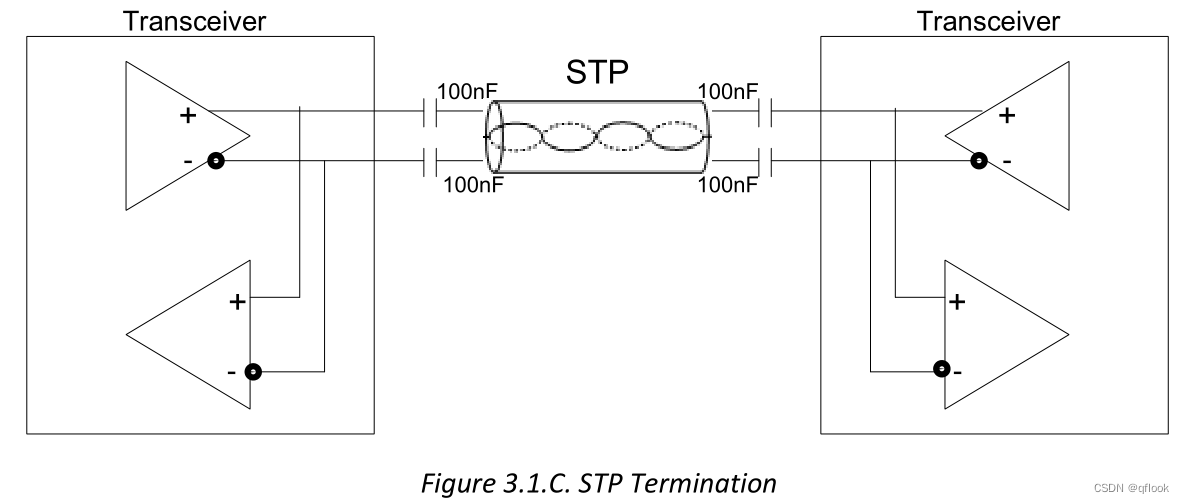

屏蔽双绞线STP模式:

positive (+)和Negative (-)管脚均被使用传输差分数据;

positive (+)和Negative (-)均使用100nF的AC耦合电容;

AC电容在不同模式下的大小选用:

同轴模式下-管脚端接方式:

AC电容放置位置(以6Gbps举例):

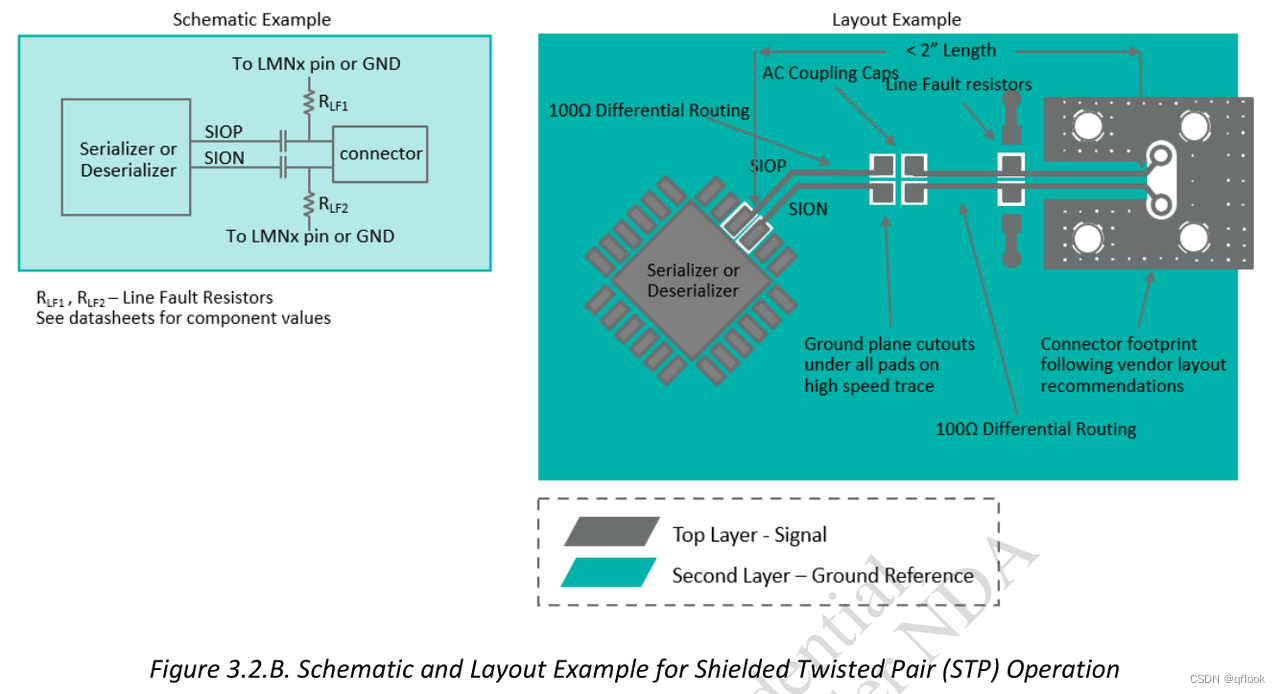

屏蔽双绞线STP的连接方式:

如有SIOA或SIOB未使用时,需要通过电容+电阻端接到GND;或者需要寄存器配置关闭。

三、PCB设计要求

PCB设计关键要求如下:

-

最短PCB走线,要求小于2英寸(5cm),插损小于1.2dB,同时PCB走线直流阻抗控制在0.1~0.2Ω/m;

-

减少阻抗不连续点,减少高速走线上的器件;

-

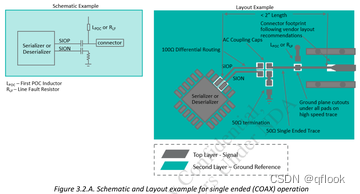

单端走线控制带50欧,差分走线控制100欧,5%精度,尽量走表层(如EMI困难可以放在内层);

-

过孔尽量少,如有则必须要有伴随地孔,差分过孔推荐两组伴随地孔;

-

AC耦合电容尽量靠近芯片(第2.2章节有具体要求),且中间不能有过孔;

-

差分走线确保等长(±5mil);

-

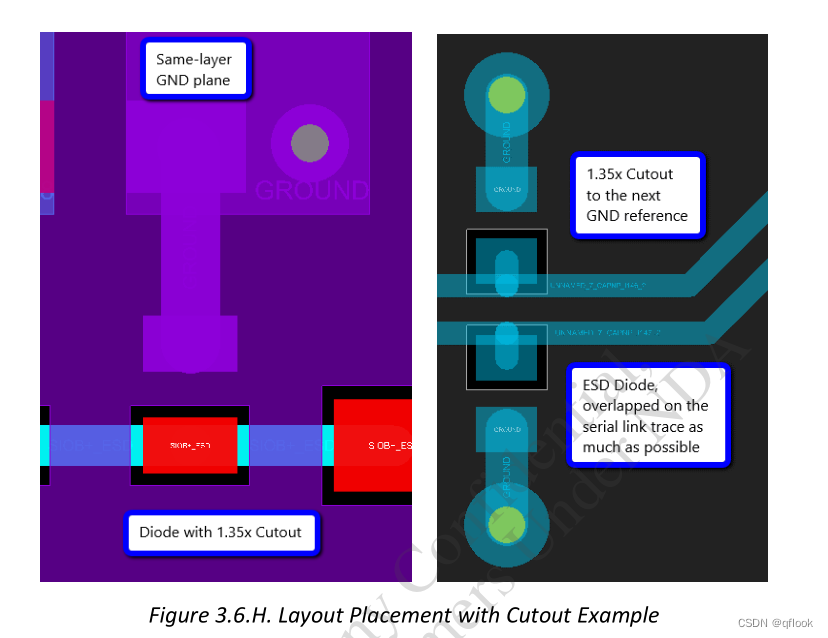

分支走线的元器件焊盘务必要放在高速走线上,且推荐焊盘内侧和高速走线内侧重合,减少stup;

-

器件焊盘尺寸大于高速走线宽度时,需要挖空下方参考层,挖空区域大小取决于层叠结构(ADI推荐1.35倍焊盘尺寸,挖空深度或者层数需根据仿真结果而定)以尽量保证阻抗连续;

-

连接器附件走线参考连接器厂商推荐PCB要求,特别是差分走线;

-

对于通孔连接器(DIP封装),推荐芯片和连接器放在不同面,以减少回波损耗;

-

芯片的接地焊盘EP需要用地孔阵列进行热管理(至少5X5阵列,推荐7X7阵列);

-

高速走线禁止弯曲90°;

-

要保持高速走线的参考层连续;

-

ESD器件要靠近连接器放置(如有POC不能使用);

-

注意高速差分信号对间距离(至少2倍间距)和差分信号对内距离(保持100Ω差分阻抗),防止串扰;

-

单端信号至少为3倍线宽,或隔离在不同的层上;

单端走线PCB实际布线举例,其中AC耦合电容和芯片之间区域协议推荐100Ω差分走线,实测不走差分,都是单端50Ω效果更好:

差分走线PCB实际布线举例:

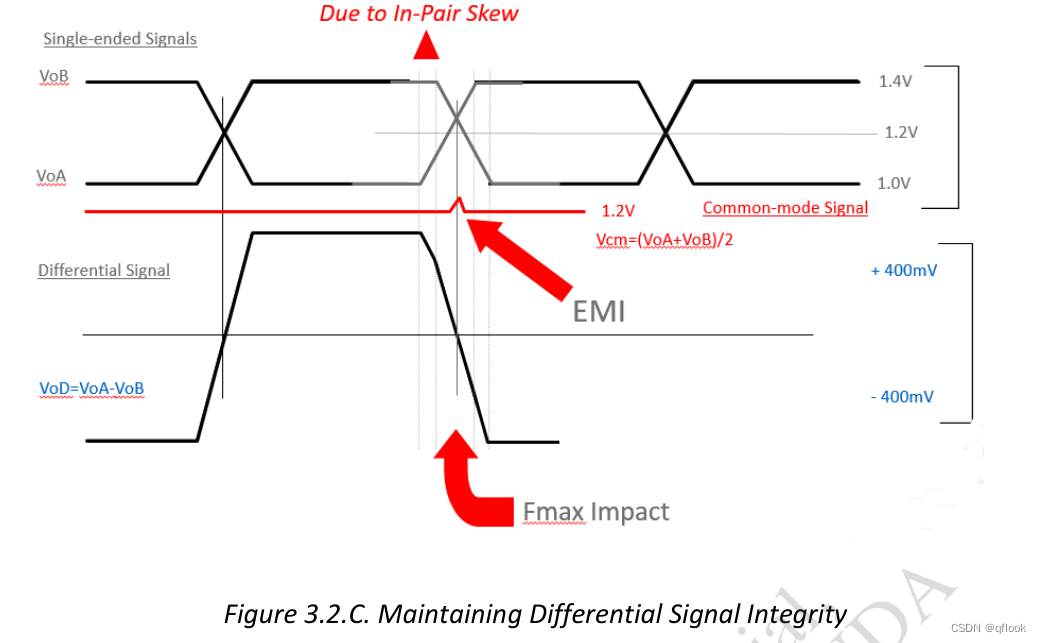

不等长引起的skew会导致EMI问题,如下:

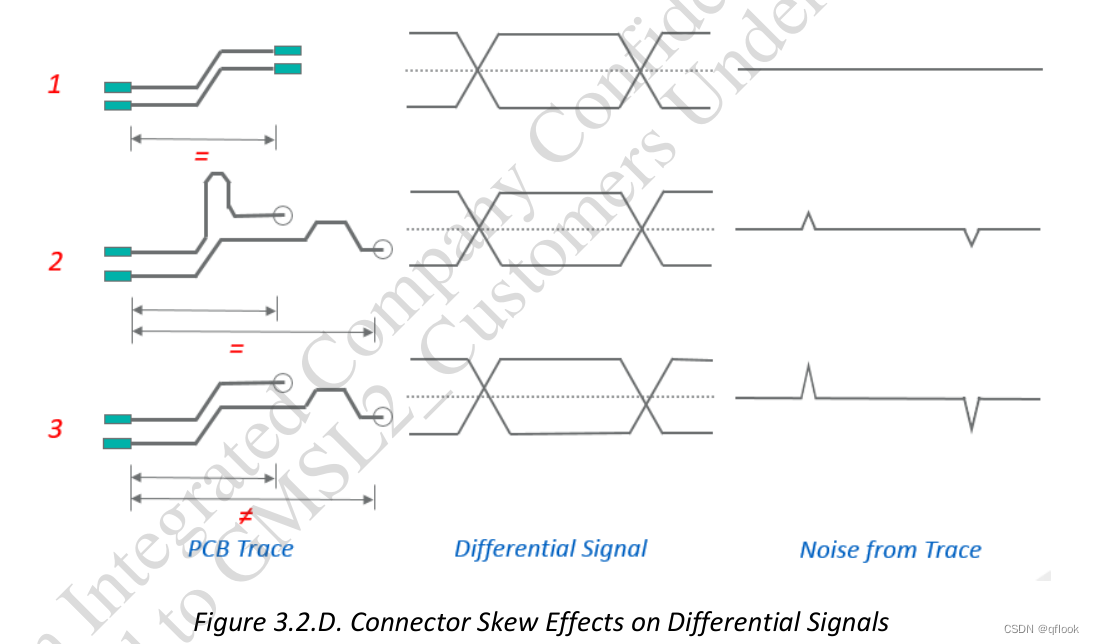

连接器skew也会引起共模干扰:

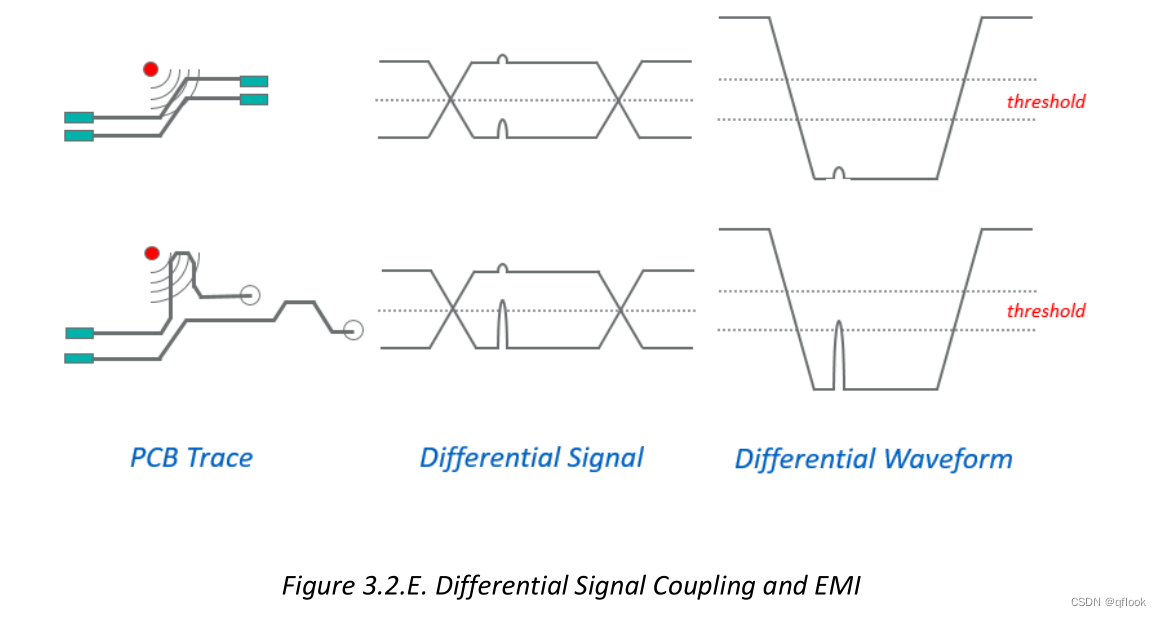

差分走线间距控制不好导致抗干扰能力下降,如下:

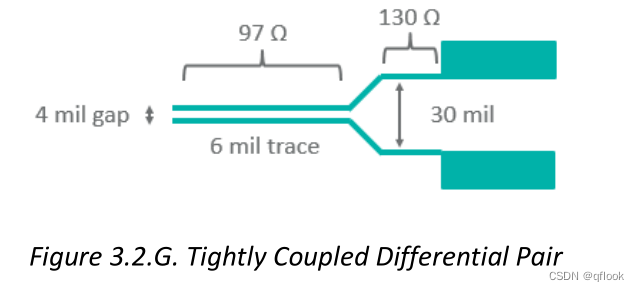

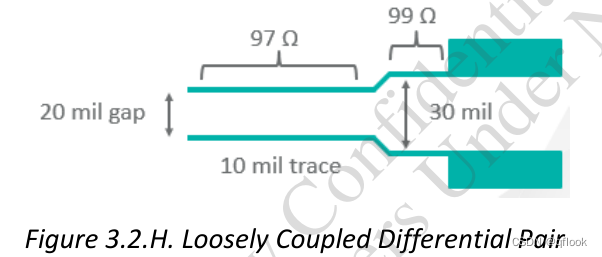

差分走线可选择紧耦合或者松耦合,紧耦合的话会有更好的EMI效果及抗干扰能力,但S参数稍差(很难保证整个链路都是紧耦合);松耦合一般会有更好的S参数,但更容易受到干扰;

三、连接器和晶振

1.连接器

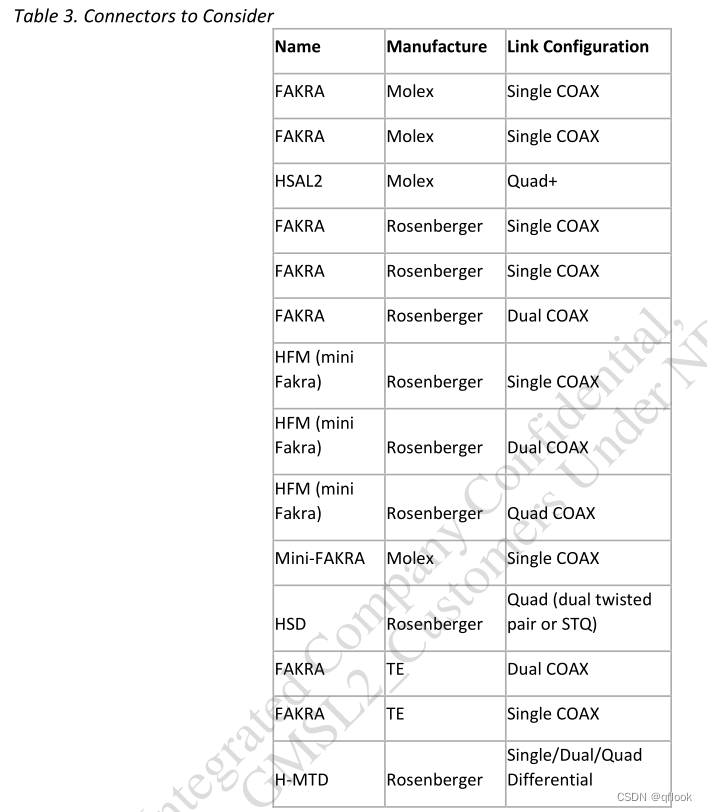

协议规范要求,连接器的插损需要控制在0.5dB以内,同时要通过3D模型仿真,来观察注意连接器引起的回拨损耗影响;推荐的连接器如下:

2.晶振

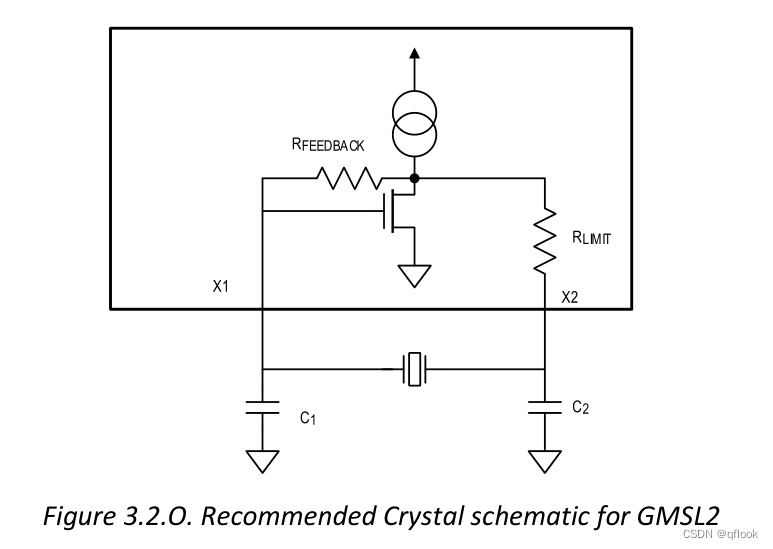

晶振要求25MHz,同时频偏和负载电容强相关,需要注意的是,负载电容包括电容值+走线电容+规格书给出的X1、X2电容值;

推荐的晶振设计电路,其中rFEEDBACK和rLIMIT是集成在芯片内部,无需外部添加:

PCB设计时需注意:

晶振尽量靠近芯片,不要求X1和X2走线等长,也不要求50Ω特征阻抗,线宽也没有要求,不过本参数会影响走线电容,需要考虑;

-

X1和X2走线推荐放在内层,避免收到GMSL2和其他GPIO的干扰;

-

如果空间允许,可以使用Ground pour工艺来改善抗干扰性能;

-

晶振外壳应保证与GND良好接触,并确保最短走线;

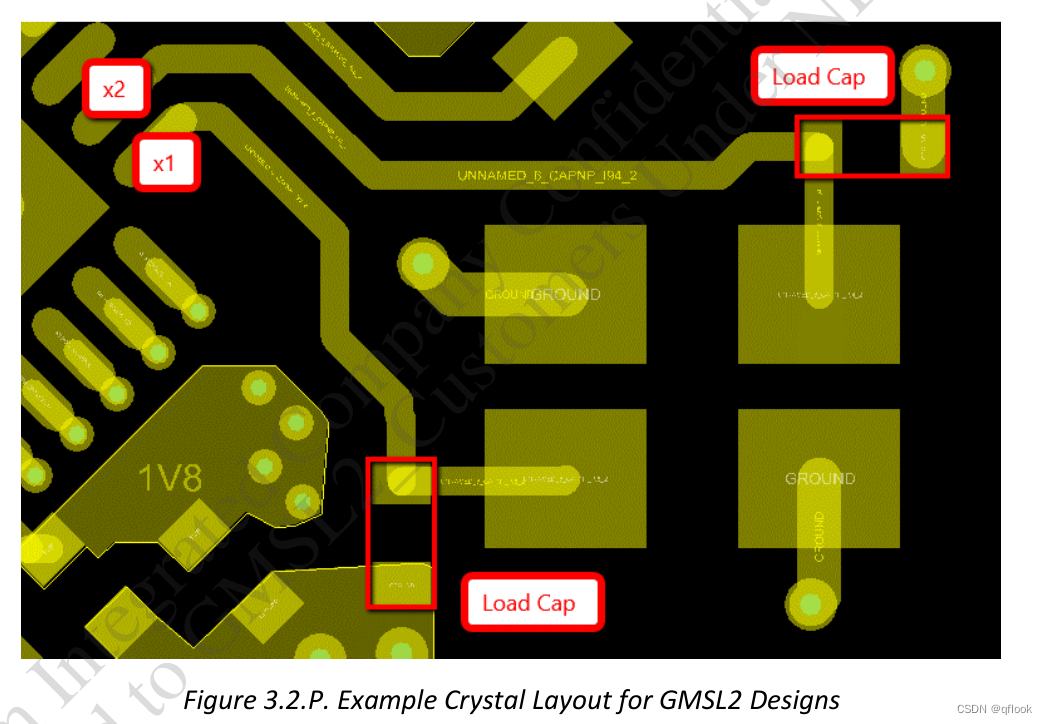

推荐的PCB布局如下:

四、线路故障和POC

1.线路故障

线路故障功能可以检测如下的故障,需特别注意的是线路故障功能和POC不能同时使用:

-

对电源短路;

-

对地短路;

-

线与线短路;

-

开路;

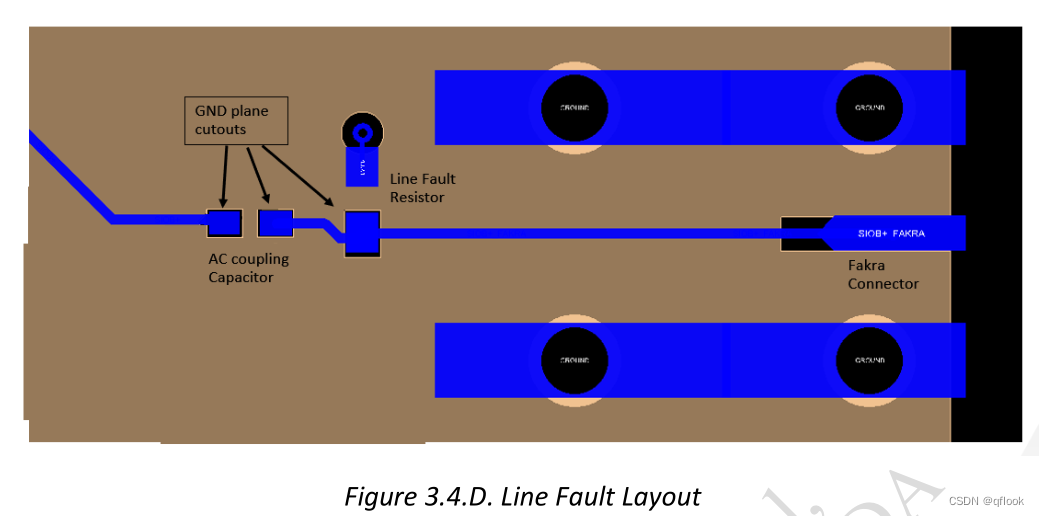

线路故障的串组要求焊盘直接放在GMSL的高速走线上,

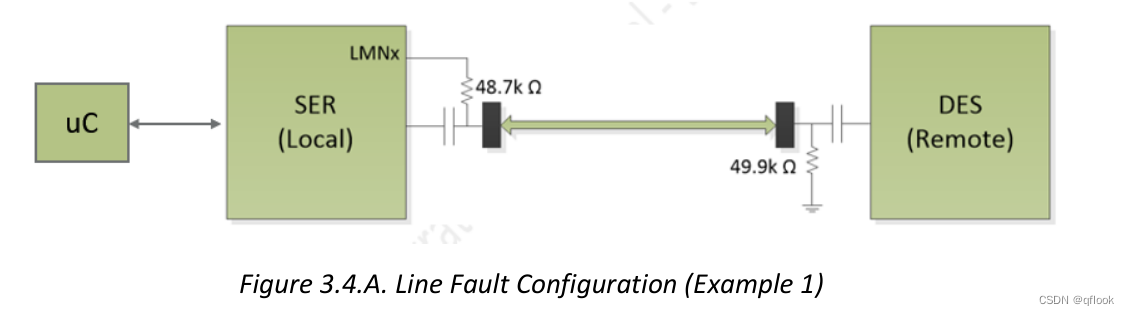

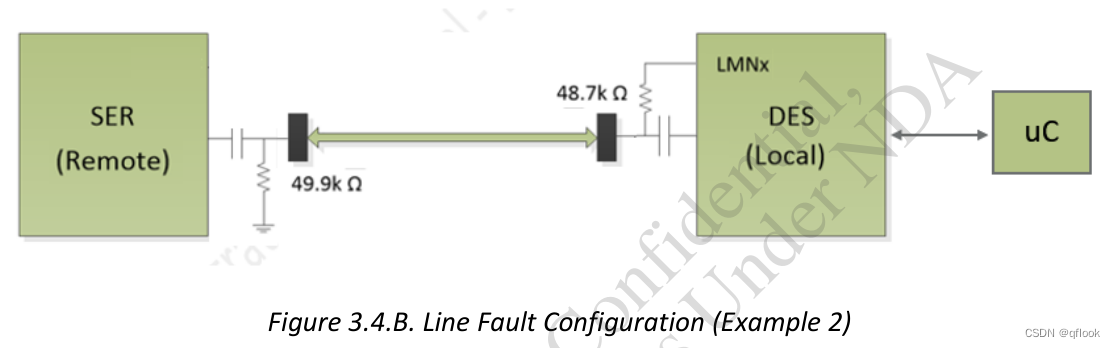

1)单端模式

线路故障需放在微控制器一侧,和是serializer还是deserializer无关。本地只需要GMSL高速走线和LMNx(一个芯片最多支持4个LMN管脚,LMN0~LMN3)之间连接一个48.7kΩ电阻即可,另外一侧需要GMSL高速走线通过一个49.9kΩ到GND即可(为了兼容GMSL1),这些电阻要求精度±3%以内;

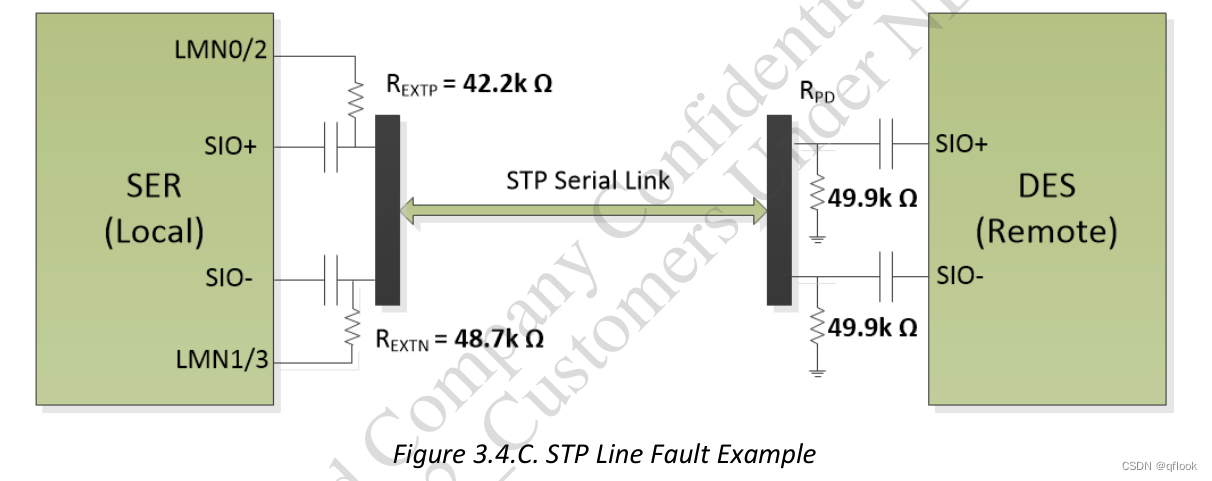

2)差分模式

差分走线的故障检测,协议要求差分走线中任意一根走线(例如P)通过42.2kΩ电阻连到偶数的LMNx(例如LMN2),另外一根差分线(例如N)需要通过48.7kΩ电阻连到奇数的LMNx(例如LMN1)。需要特别注意的是线与线短路只能LMN0和LMN1或者LMN2和LMN3配对时检测,因此推荐这种配对方式。远端仍然是49.9kΩ电阻接地,同时要求这些电阻要求精度±3%以内。

线路故障电阻在PCB上布置,需要一端焊盘放置在GMSL高速走线上,并在下方参考层挖空,以保证阻抗连续:

2.POC

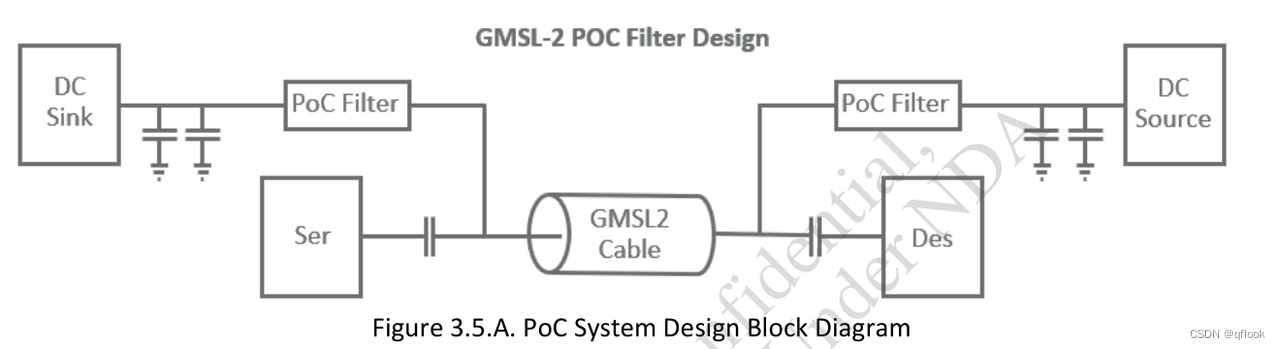

POC(Power over Coax同轴电缆供电)技术就是在同轴电缆上可以同时传输电源和数据,优点是可以节省对端设备的电源供电电路,常用于摄像头。供电需要大电流(影响器件选型),输送数据需要高带宽,故设计需要考虑RF和功率器件的结合,设计难点也主要在此。

POC的滤波器会影响GMSL的插损和回损,好的POC设计应能保证在前向通道和反向通道有效频带范围内都有比较好的性能。

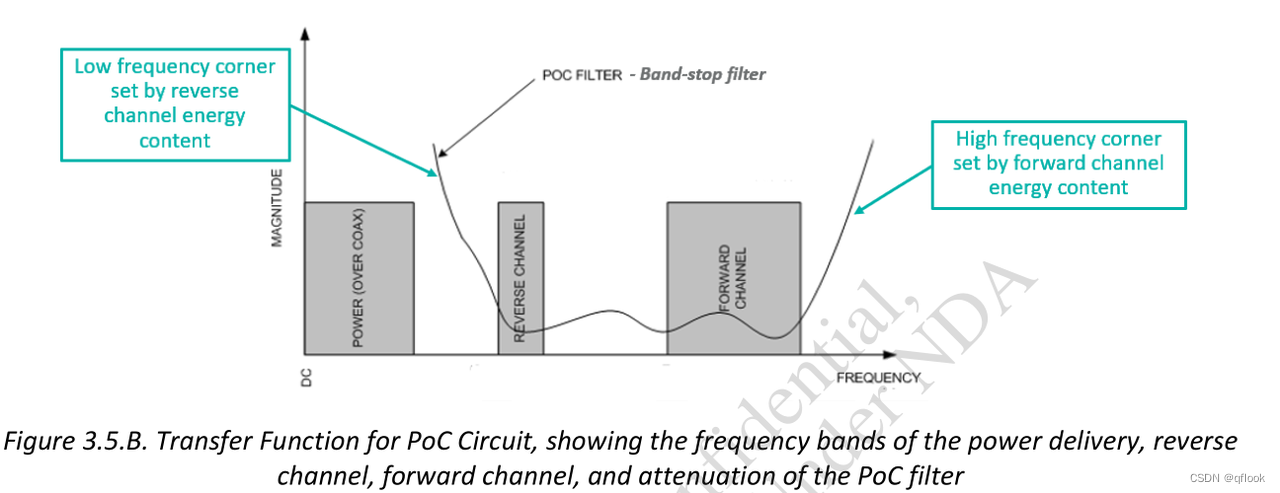

POC滤波器是一种陷波滤波器(notch filter),可以允许DC通过,阻止GMSL高速数据有效频段内信号;而AC耦合电容则可以通过高速信号,阻止DC直流。

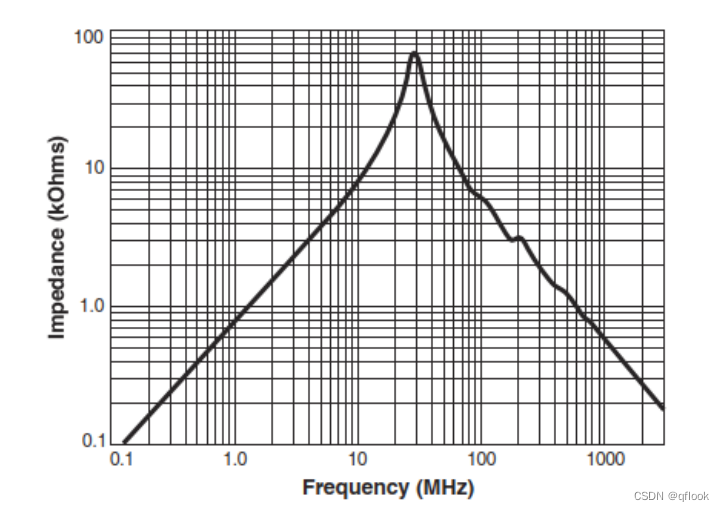

一个典型电感的频率-阻抗曲线如下:

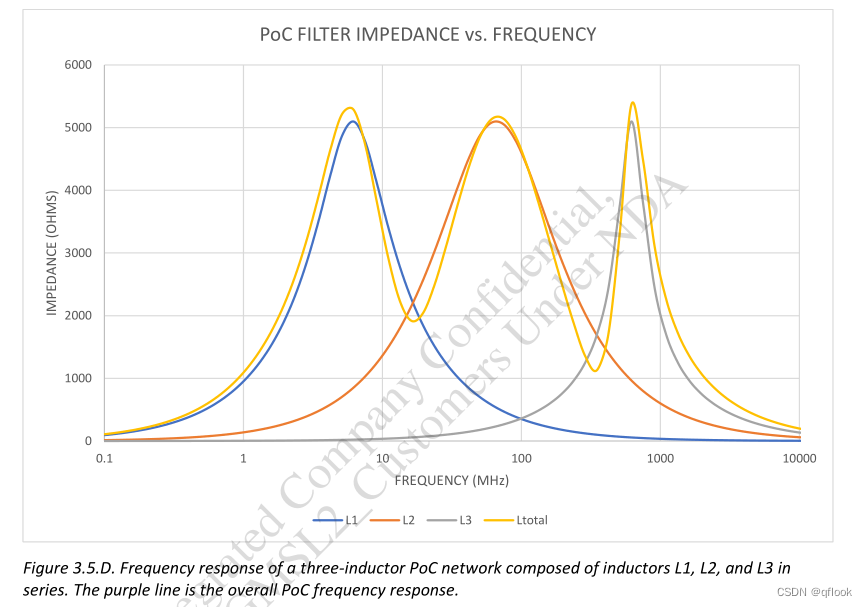

由上图可知,单个电感是无法覆盖GMSL前向和反向通道有效带宽的,因此需要多级电感串联组成一个滤波器,理想的滤波器如下(三级电感串联),另外ADI不推荐使用铁氧体磁珠:

协议规定,为了保证插损和回损指标,要求在7M~3G频带内POC滤波器阻抗不低于1kΩ;电感值随着直流电流的增加而下降,推荐饱和电流对电感的影响不超过零电流值的10%;另外协议建议选型电感的直流阻抗尽量低(影响DC压降和发热)。

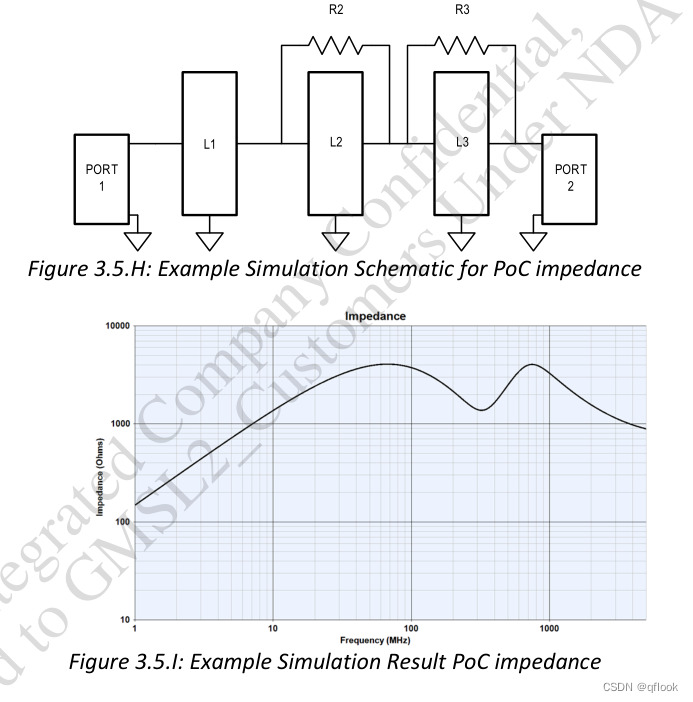

POC滤波器设计较难,协议推荐首先进行仿真,有效减少改版次数,提高设计成功率。举例如下:

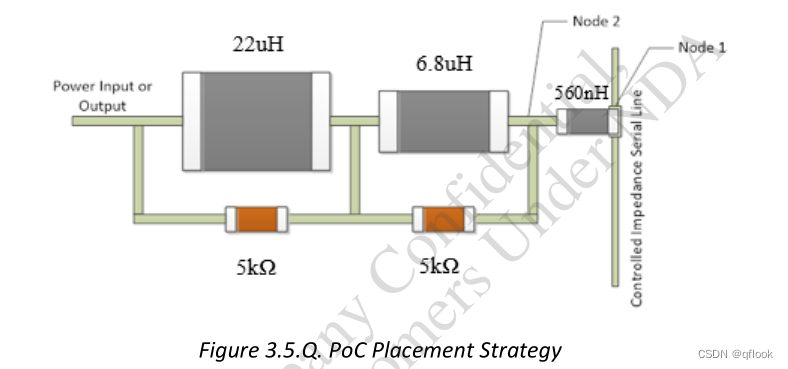

协议推荐,POC电路全部器件放在同一层,不能有过孔,防止过孔带来的频响效应;布局策略如下(其中具体电感、电阻协议也有推荐,实际常用的是1.5K并联电阻,改善Q值,具体参考协议规范):

其他建议:

1)第一级滤波电感垂直放置在GMSL高速走线上;

2)各级滤波电感直接距离尽量短,也就是各个电感尽量靠近;

3)电感和POC电源直接电容也要靠近电感,否则易引起3G以上频段的波动;

4)各级电感要挖空,层数越多越好(放置在高速走线的焊盘除外,这个地方要考虑50Ω阻抗匹配);

五、测试

1.线材

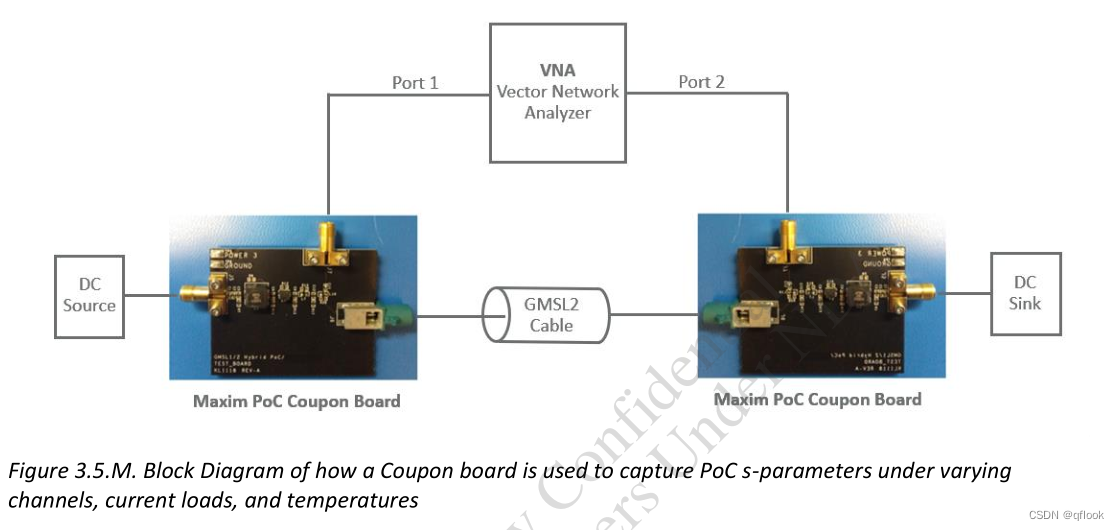

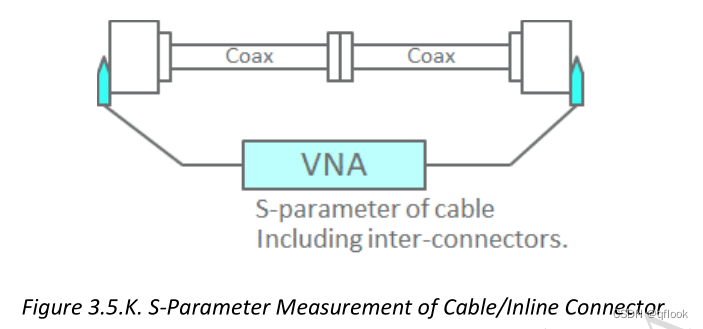

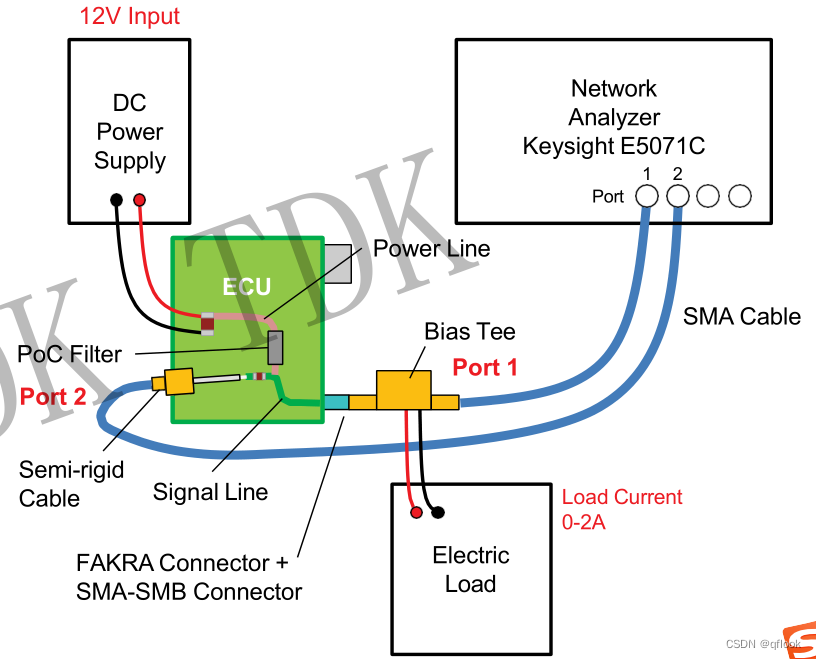

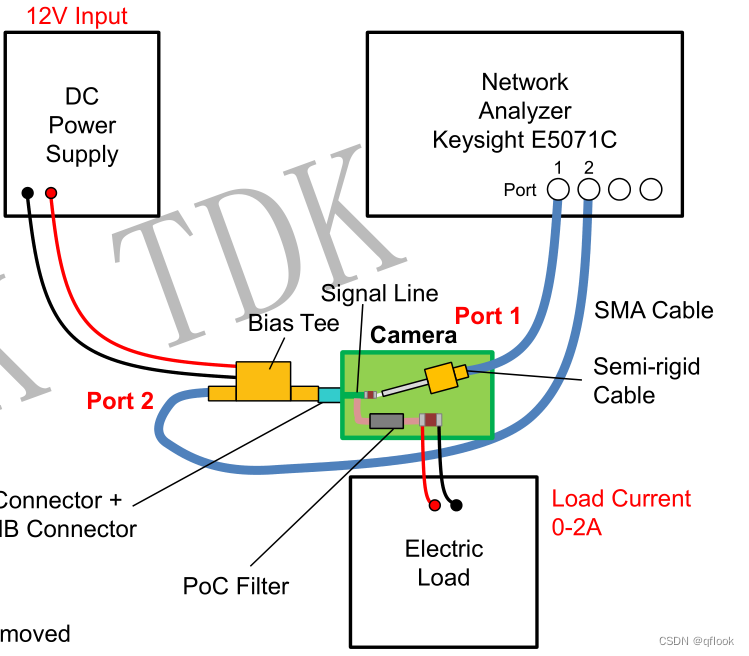

带POC影响的线材S参数测试框图如下:

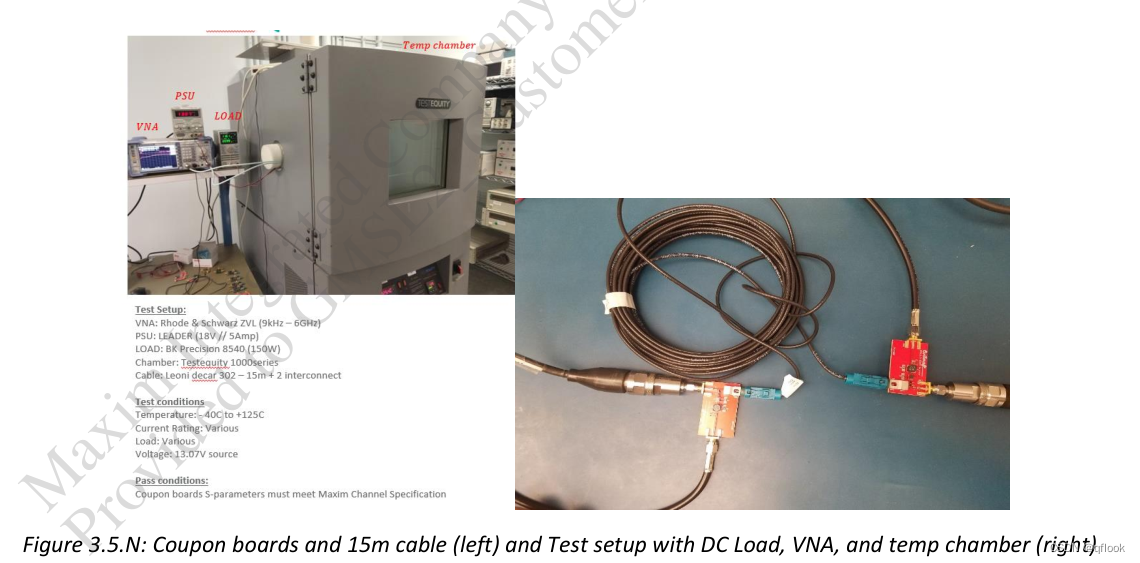

实测需要考虑环境温度的影响,如下:

如无POC,则使用网分直接测试即可,另协议推荐考虑最坏情况,使用老化的线材测试:

2.系统

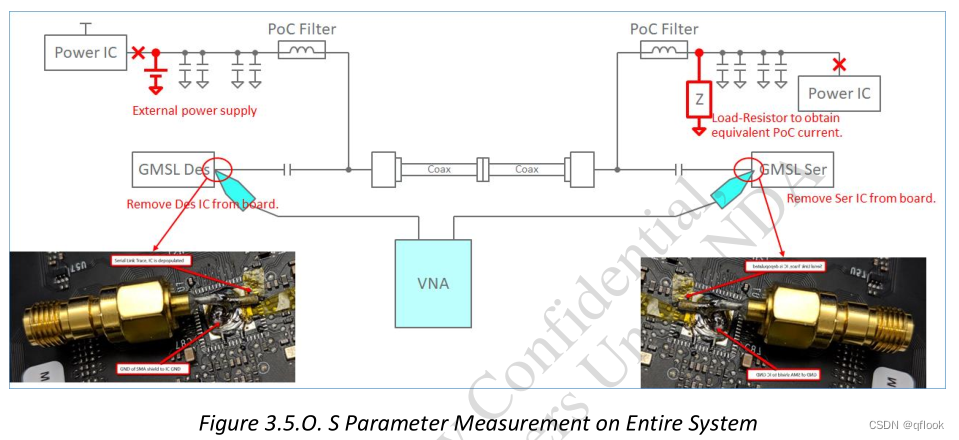

系统S参数测试框图如下,其中测试时GMSL芯片都需要去掉,然后焊接SMA同轴电缆到对应焊盘上;电源芯片和POC负载也需要去掉,使用外部电源单独供电(务必在POC滤波器之前,提供最大电压和最大电流),然后负载根据最大电流在另外一个POC滤波器后加相应电子负载即可:

3.单板

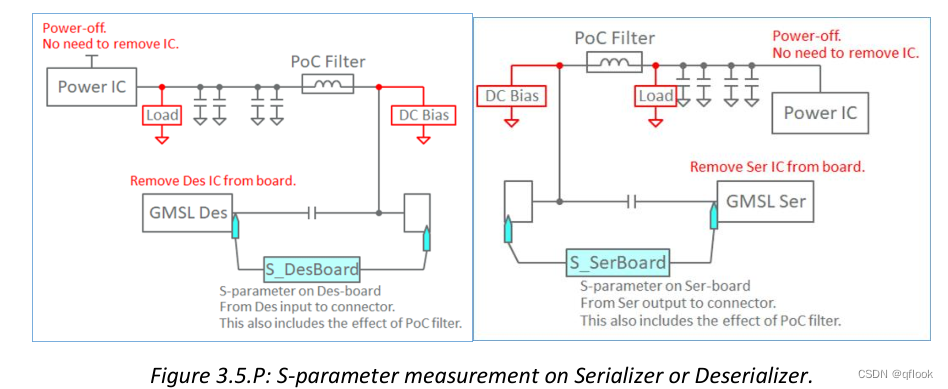

PCB带POC的S参数官方规定测试系统如下:

这个测试环境个人认为有问题,其一是DC电源需要和load互换位置,否则滤波器无用了,其二是网分在连接器处需要增加一个隔直器,防止网分损坏,因此比较推荐TDK的测试环境。

POC源端测试环境:

POC的sink端测试环境:

4.ESD

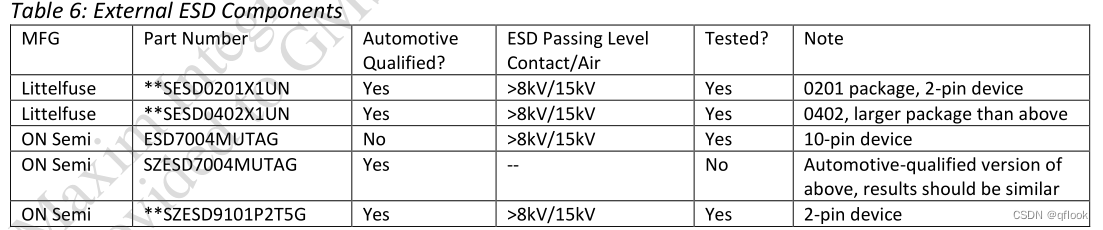

ADI的GMSL芯片有一定的ESD防护能力,如需要更好的保护水平才需要单独的ESD器件,否则可以不加。如需要外J加ESD时,需要:

-

等效电容小于0.5pF;

-

封装尽量小(推荐0201);

-

低击穿电压和低钳位电压(小于10V);

-

推荐单向TVS(不建议使用双向TVS);

-

采用双端口的器件;

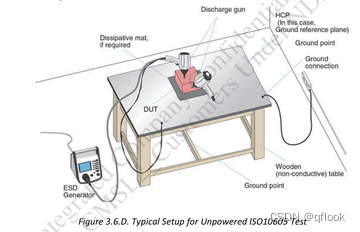

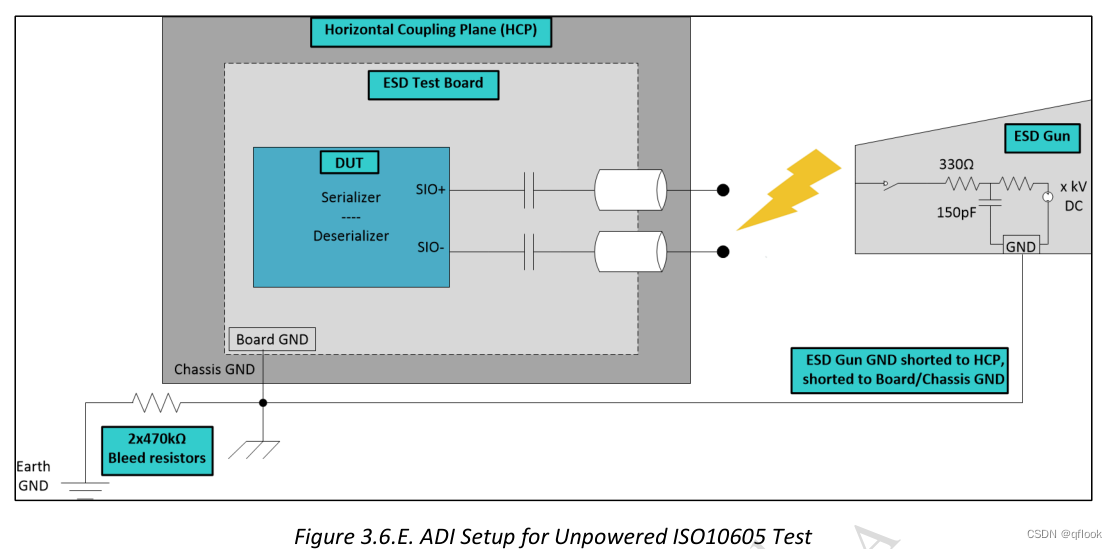

ADI采用ISO10605标准进行ESD测试,系统搭建如下:

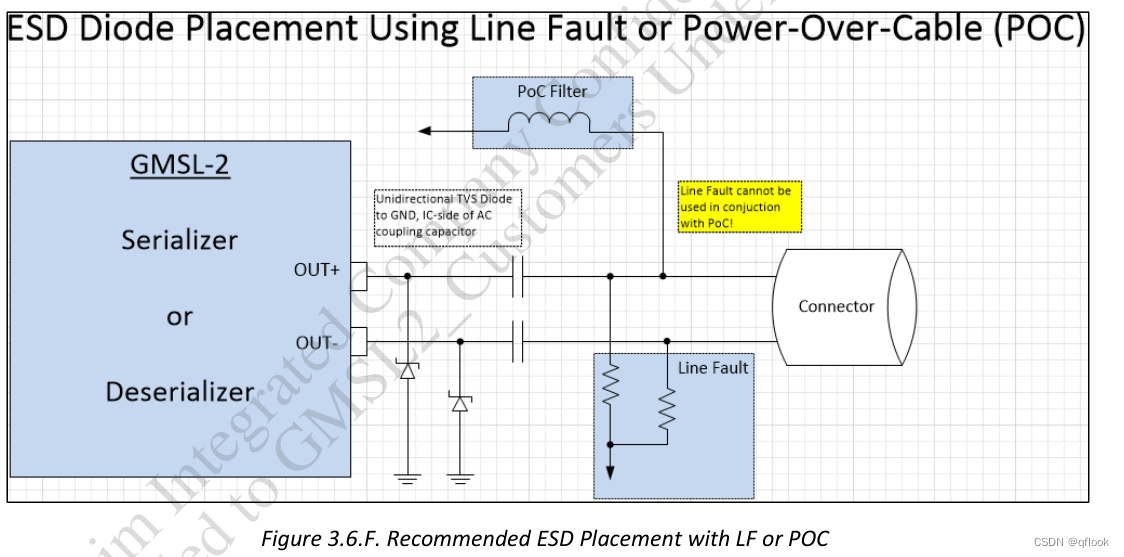

对于使用线路故障检测功能或者POC的情况,TVS(如果需要的话)需要放置在芯片和AC耦合电容之间,原因是对电源短路或POC供电情况,高速总线上电压较高会导致TVS损坏,若选取耐高压的TVS的话,一般寄生电容会比较大影响插损和回损;

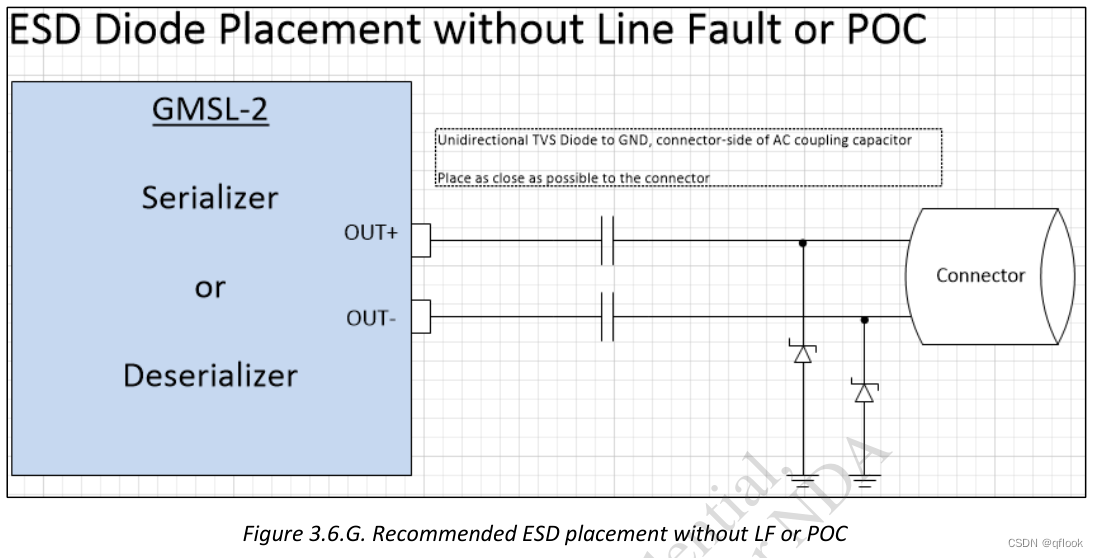

如不使用POC或line fault则推荐TVS放在连接器处,如下:

ADI推荐了部分TVS器件如下:

TVS的推荐PCB处理如下:

一般原则:

-

芯片远离潜在的ESD事件源;

-

禁止TVS引起stub;

-

TVS接地路径尽可能短;

-

如果TVS放置在连接器处,就应该尽可能靠近连接器;

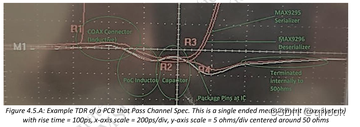

5.TDR

TDR(Time-Domain-Reflectometer)用来测量整个传输线各点的特征阻抗,测试时需要设置激励的上升时间为0.35/带宽,例如GMSL2的6Gbps速率时,协议明确给出有效带宽至3.5G,因此上升时间就是100ps(10%~90%);同时协议指出在规定上升时间的激励信号的情况下,要求传输线阻抗的范围是±10%,也就是单端传输线是45~55Ω,差分传输线是90~100Ω。

当然,上升时间也可以更短(推荐20~50ps),这种设置有更好的分辨率,在精确查找阻抗不连续点或者优化阻抗匹配时更明显。

单端传输线从连接器往芯片方向,阻抗不连续点分析距离如下: