系列文章目录

目录

- 数字逻辑基础

- 一个基本的MIPS实现

- 核心子集与指令周期

- 数据通路设计

- 取指令周期 IF

- 译码与读寄存器周期 ID

- 运算周期EX

- 访存与分支周期MEM、写回周期WB

- 增加多选器

- 指令周期小结

- 控制信号设计

- ALU 控制线

- ALU控制单元

- 主控制单元

- RegWirte、RegDst、ALUSrc

- MenWrite、WemRead、MentoReg

- PCSrc

- 控制信号小结

- 带控制信号的数据通路

数字逻辑基础

根据是否含有存储器, 数字逻辑部件分为两类:

- 组合逻辑不含存储器,单纯对数据进行操作,给定输入时输出唯一确定

- 状态逻辑(时序逻辑)含有存储器,至少有两个输入:时钟、代写数据——和一个输出:存储的数据只有在时钟信号的上升沿,才允许向状态单元写入数据,这样的时钟方式称为边沿触发的时钟

多选器(MUX)从多个数据中选择一个作为输出,选择哪个数据取决于选择控制信号

总线(BUS)表示数据信息多于一位的信号线

一个基本的MIPS实现

核心子集与指令周期

我们将要设计的实现方式包含了 MIPS 指令集的一个核心子集:

- 存储器访问指令:取字 (lw) 和存字(sw)

- 算术逻辑指令:加法 ( add ) 、减法 ( sub) 、 与运算 (AND) 、或运算 (OR) 和小于则设置 ( slt)

- 分支指令:相等则分支 (beq) 和跳转(j),我们放到最后实现

使用这个MIPS子集可以说明建立数据通路和控制单元的关键原理,和其他体系结构是相通的

一条MIPS指令的执行分为五个阶段,统称为一个指令周期(instruction cycle)

- IF 取指令:根据PC所给地址,从存储器中取出指令

- ID 译码与读寄存器:分析指令字段,读取一个或两个寄存器

- EX 运算:ALU运算R型指令的结果/访存指令的地址/beq两源操作数是否相等

- MEM 访存与分支:访存指令向存储器进行读写,分支指令完成分支

- WB 写回:将结果送回某寄存器

数据通路设计

取指令周期 IF

IF 取指令任务:根据PC所给地址,从存储器中取出指令

我们将存储器中的指令和数据分别看待,由此形成指令存储器和数据存储器

指令存储器存放程序的指令,输入一个地址时输出其指向的指令

程序计数器(PC)保存当前指令的地址

我们将一个ALU完全用作加法器(Add),用来计算PC+4,即下一条指令的地址

译码与读寄存器周期 ID

ID 译码与读寄存器任务:分析指令字段,读取一个或两个寄存器

- 寄存器堆(reg file)含有32个通用寄存器

- 对应R型指令的三操作数格式,寄存器堆接收3个寄存器编号

- 其中至多两个寄存器用于读(R型和beq读两个,sw读一个)

- 至多一个寄存器用于写(R型写回rd、lw写回rt)

- 读取时输出rs和rt寄存器中的数据

- 为了支持写入数据,需要一个32位的写数据端口作为输入

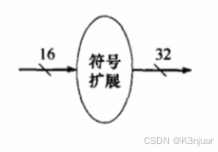

- 符号扩展

- 访存指令中的16位偏移量(立即数)和beq中的相对地址需要经符号扩展(sign-extend)逻辑扩充到32位

- 对访存指令,这个数和rs中的基地址相加

- 对beq指令,需要一个移位逻辑将字地址转换为字节地址

运算周期EX

EX运算周期任务:ALU运算R型指令的结果 / 访存指令的地址 / beq两源操作数是否相等

(作出IF、ID、EX阶段的局部数据通路)

- 对于R型指令,ALU执行相应的算数 / 逻辑运算,并输出结果

- 对于访存指令,ALU计算基地址和偏移量的和,得到数据的真正地址

- 对于分支指令,ALU将两源操作数相减,根据结果是否为0,判断两数是否相等,与此同时,加法器得到符号扩展并左移两位的PC相对地址,将其与PC+4相加得到分支目标地址

访存与分支周期MEM、写回周期WB

MEM访存分支任务:访存指令向寄存器进行读写,分支指令完成分支

WB写回任务:将结果送回寄存器

-

访存指令在第四阶段才真正读 / 写数据存储器

- ALU计算基址和偏移量的和,得到真正地址并输入数据存储器

- lw从数据存储器读取数据并输出,sw向数据存储器写入数据

-

beq分支指令在这个周期不访存

- 但会选择将PC+4(第一阶段)或分支目标(第三阶段)写回PC,决定分支是否发生,因此,将第四阶段称为访存分支周期

第五阶段,R型指令将运算结果写回rd寄存器,lw指令将存储器数据写回rt寄存器

增加多选器

上面的一些指令会导致输入的多种选择,主要如下:

- beq指令导致输入PC的是PC+4还是beq分支

- 指令中含有立即数(addi $s1, $s2,12;lw $s1,20( $s2 );beq $s1, $s2, 20)导致ALU计算时输入的是寄存器rt还是32位立即数

- 写回寄存器时,R型指令是将ALU计算结果写回rd,lw指令是将数据存储器从内存中取出的数写到rt

- 对于是存ALU计算结果还是存数据存储器取出的数据 ,需要一个外部多选器

- 对于是存到rd还是rt可以直接在寄存器堆内部进行选择,可以不需要在外部加多选器

加上多选器后,最终数据通路如下图

指令周期小结

- 单周期实现中,每条指令都在一个时钟周期内完成,CPI为1

- 注意到只有lw使用全部5个阶段,因此基本可以肯定,时钟周期取决于lw的执行时长

- 其他指令只用4个阶段,但仍然要花费5个阶段的时间

- 多周期实现可以缩减时钟周期到1个阶段的长度,一条指令占用几个阶段,就执行几个周期

- 虽然CPI变成了4或5,但时钟周期缩短到1/5,运行速度反而更快

- 虽然CPI变成了4或5,但时钟周期缩短到1/5,运行速度反而更快

控制信号设计

ALU 控制线

ALU可以执行加add、减sub、与AND、或OR、小于则置位slt五种运算,具体执行什么运算,由4位ALU控制线决定

ALU控制单元

主控制单元根据指令操作码(指令开头6位op),向ALU控制单元输出一个2位控制信号ALUOp(ALU操作码)

- 当ALUOp为00时,表示这条指令是访存指令,需要ALU将基址和偏移量相加(0010)

- 当ALUOp为01时,表示这条指令是分支指令beq,需要ALU将两源操作数相减(0110)

- 当ALUOp为10时,表示这是条R型指令,由funct字段进一步指定需要ALU完成的功能

- 判定为R型指令后,ALU控制单元将6位功能码funct字段映射到加0010、减0110、与0000、或0001、小于则置位0111中的一个

- ALU控制线由主控制单元发出的ALUOp、R型指令中的funct字段两级共同决定,这种多级译码方式有利手提高控制器性能

主控制单元

RegWirte、RegDst、ALUSrc

-

指令寄存器

- 一个程序在运行前将指令写入指令存储器,不需要专门的写使能控制信号来“批准”写入指令存储器每周期进行一次读操作

- 是只读且必读的,不需要专门的读使能控制信号来“批准”读出

-

寄存器堆

- 8条MIPS核心子集指令都会读寄存器,无需读使能控制信号

- 但是,只有R型指令和Iw指令会写回寄存器堆,因此要有寄存器堆写使能控制信号 R e g W r i t e RegWrite RegWrite

- 并用启用 r d rd rd控制信号 R e g D s t RegDst RegDst决定写回 r d rd rd还是 r t rt rt

-

ALU

- 对ALU,除了上述两位ALUOp信号,还需要启用立即数(作为ALU源)控制信号ALUSrc

- 为1时选取符号扩展后的立即数作为ALU源操作数

- 为0时选取rt作为ALU源操作数

- 对ALU,除了上述两位ALUOp信号,还需要启用立即数(作为ALU源)控制信号ALUSrc

MenWrite、WemRead、MentoReg

- 数据存储器

- 只有lw读数据存储器,只有sw写数据存储器

- 因此,数据存储器需要读、写控制信号各一个:

- (数据)存储器读使能控制信号 M e m R e a d MemRead MemRead

- (数据)存储器写使能控制信号 M e m W r i t e MemWrite MemWrite

- 因为指令存储器不需要读写使能控制信号,不必强调是“数据”存储器

- 写回

- R型指令从ALU写回寄存器,lw从存储器写回寄存器,为了选择写回寄存器的数据来源,需要一个存储器写回控制信号MemtoReg

- 为1时将存储器数据写回

- 为0时将ALU运算结果写回

PCSrc

分析分支指令beq使用的控制信号

- 仅当遇到beq指令才可能分支

- 分支条件为真,即ALU运算 r s − r t = 0 rs-rt=0 rs−rt=0时才分支

使用一个与门(AND gate)进行与运算

- 当分支控制信号Branch和ALU零标志Zero同时为真,将PC源控制信号PCSrc置为1,选择将分支目标地址写回PC,完成分支

- 只要其中一个条件为假(包括两个都为假),选择PC+4写回PC,取消分支

控制信号小结

指令周期第二阶段的指令译码,就是主控制单元将操作码(Op,不包括funct)翻译成控制信号,并发射到对应器件的过程

经过主控制单元以及后续处理,最后能得到8个控制信号(共九位),由Op与funct翻译而成(最后包含funct)

注意主控制单元只发出Branch信号,不直接发射PCSrc信号

带控制信号的数据通路