1. EtherCAT 主站的硬件组成

EtherCAT主站使用标准以太网控制器,也即EtherCAT主站可以使用以太网控制器的任何设备。当我们有一台带网口的笔记本、工控机,甚至是树莓派也可以作为EtherCAT主站。

EtherCAT协议是对Ethernet协议在实时控制等方面的优化,因此对于一个能够支持Ethernet通信的设备,就可以支持EtherCAT协议的实现。

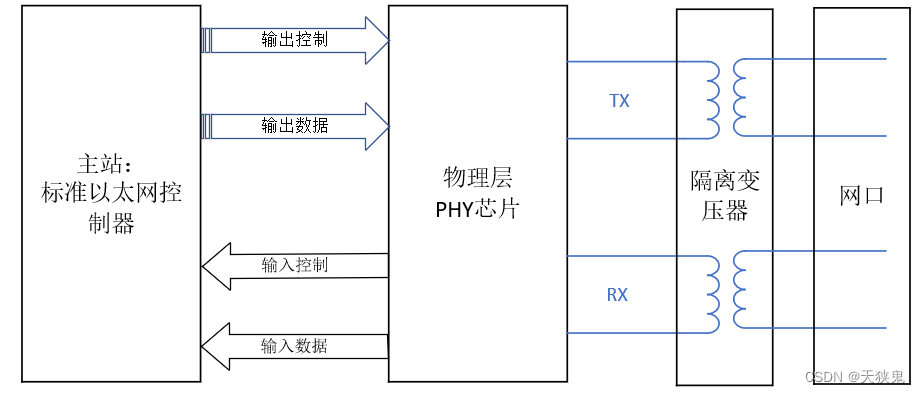

EtherCAT主站的组成:

其中

以太网控制器完成以太网数据链路的介质访问控制功能(MAC, Media Access Control Twisted Pair)。

PHY芯片主要完成数据的编码、译码和收发的功能。

事实上,上述的结构是一个网卡的组成结构。EtherCAT主站还需要包含其软件部分,EtherCAT主站通常是纯软件实现的,不需要任何专用的硬件。如果在嵌入式主站中,通信控制器通常被嵌入到微控制器中,链接是在Zynq上实现EtherCAT主站的一些介绍。

2. EtherCAT从站硬件组成

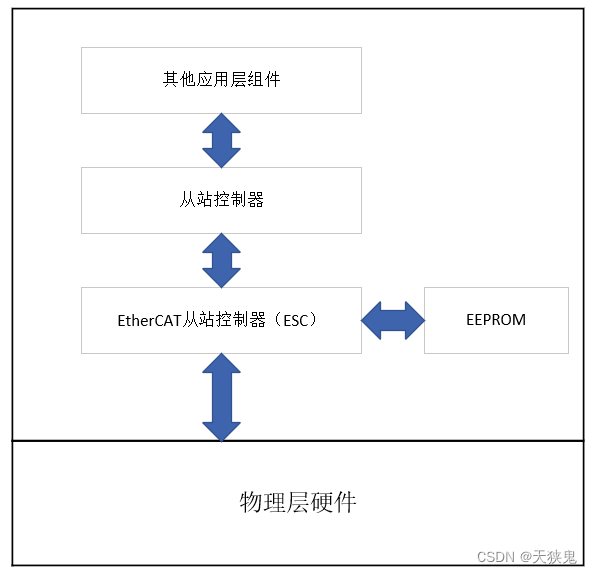

EtherCAT从站一方面实现与主站的通信,另一方面完成控制或信号处理功能(这取决于从站功能定义)。因此需要对两部分进行区分。

2.1 从站控制器

从站控制器负责与EtherCAT从站控制器(ESC)做数据交换并完成控制和信号监测任务。从站控制器更像是一个物理模块的MCU,一方面通过 ESC 读取主站发送的控制参数,或将自身的数据发放到ESC上,然后通过主站读取。另一方面控制着硬件模块的执行动作或采集数据。

2.2 ESC:EtherCAT从站控制器

为确保通信效率和实时性,ESC完全负责与主站的通信过程。EtherCAT报文经过从站时,ESC从报文中提取发送给自己的输出命令数据,并将其存储到内部存储区。ESC同时会将需要写给主站的数据写入相应的子报文中。数据的提取和插入都是由数据链路层硬件完成的。

ESC使用两种物理层接口模式:MII 和 EBUS。 MII时标准的以太网物理层接口。而EBUS是德国倍福公司开发的基于LVDS标准的数据传输协议,比如倍福IO模块的耦合,绝大多数使用这种接口。

ESC芯片通常使用ET1100,也有其他型号的从站控制芯片,当使用MII方式时,必须要使用PHY芯片和隔离变压器等标准以太网物理层器件。

3. ESC专用芯片与FPGA IP-Core

ESC作为EtherCAT从站数据链路层协议的专用集成芯片,是开发从站不可获取的元件。ESC的硬件部分可以使用ASIC芯片或IP-Core来实现。

ASIC: 专用集成电路

IP-Core:FPGA的IP核,用于实现某些功能,这里专门实现ESC相关功能

3.1 ESC ASIC芯片主要特性(ET1100为例)

端口:4个端口,EBUS/MII

FMMU:Fieldbus Memory Management Unit,现场总线内存管理单元,8个

存储同步管理单元:3个

过程数据RAM:8KB

分布时钟:64位

物理设备接口(PDI):32bit数字量IO, 8/16bit 异步/同步微处理器接口、串行外设接口

EEPROM:16KB

封装:BGA128, 10mm * 10mm

3.2 以IP-Core方式实现ESC

Altra公司的ET18xx IP core可用于ESC。

Altra公司已于2015年被Intel收购,因此尚不确定该IP-Core是否还能使用

需要注意的是:IP-Core可以用于实现ESC功能。

—— 主站与从站的硬件组成)