参考来源:JESD209-4B,JESD209-4E

LPDDR Initial → LPDDR Write Leveling and DQ Training → LPDDR Read and Training → LPDDR Write and Training → LPDDR Power Down → PIM Technical

Write Leveling

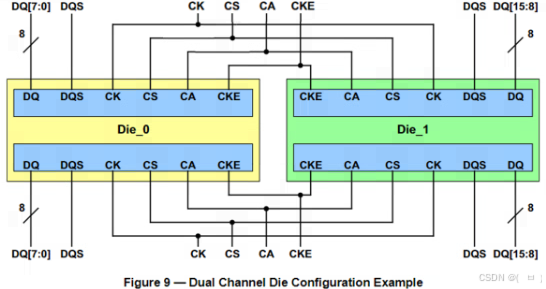

先看下JESD209-4E中Figure 9对LPDDR4下信号线拓扑结构的描述,理解为什么需要Write Leveling。

可以看到不同DRAM的DQ/DQS信号都是分开独立的,所以不同DRAM之间不会存在太大DQ/DQS信号延时差异。

但是Address/Command/CLK信号在Fly By结构下传输到不同DRAM过程中势必存在不同的延时。

所以通过Write Leveling调整不同DRAM上DQS-Data Strobe输入信号相对于CLK信号的延时,从而能够在不同DRAM CLK Delay下采样到正确的DQ Data。

DQS信号由MC控制器驱动,DRAM在DQS边沿采样CLK信号。

DRAM通过提供有关DQ上捕获的CLK电平的反馈来响应MC控制器。

通过DRAM反馈确定DQS相对于CLK是超前还是滞后,从而调整Delay的增加或者减少。

以下是每个DRAM上Write Leveling详细过程:

- 配置MR2寄存器进入Write Leveling Mode

- 当DRAM检测到稳定的DQS信号,就对当前CLK采样,再把CLK Value通过DQ Bus返回MC

- MC控制器根据反馈调整DQS延时数值,等待一段时间后发送下一组DQS信号

- DRAM重复CLK采样并返回给MC,直到MC确认可以捕获到稳定的CLK信号

- 配置MR2寄存器退出Write Leveling

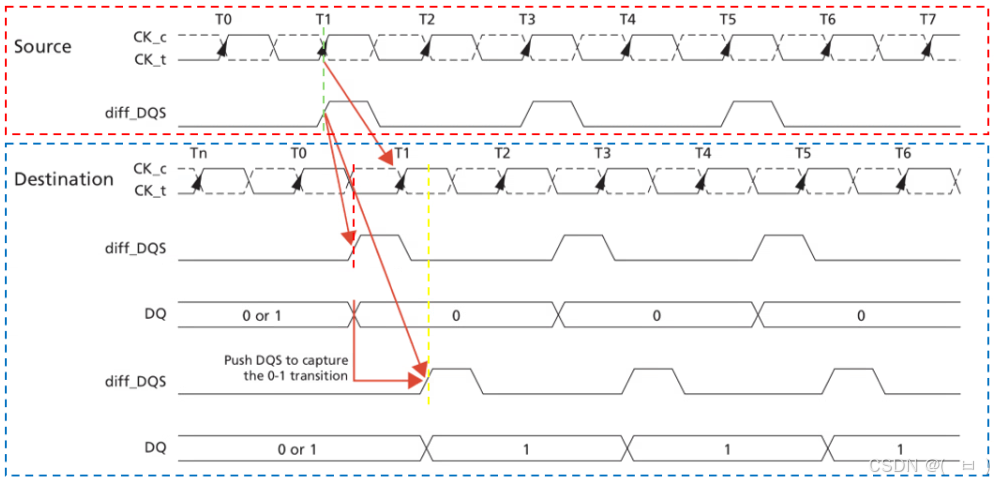

下面是Write Leveling过程的示意图:

可以看到Source侧(红色虚线框)的CK信号与DQS信号彼此的上升沿是对齐的(绿色竖向虚线)。

到了Destination侧(蓝色虚线框),出现了DQS信号上升沿不再对齐CK信号的情况。

DRAM采样此时的Clock Value = 0(红色竖向虚线),通过DQ Bus返回给MC控制器。

MC控制器调大Delay,再次发送DQS,DRAM再次采样Clock Value = 1(黄色竖向虚线),返回给MC控制器,确认Delay满足需求。

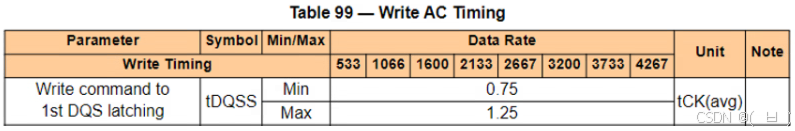

在JEDEC规范中tDQSS的限制,就是Write Leveling后,CLK和DQS之间skew的Limitation区间:

SIPI测试中tDQSS的测试细节会在之后的LPDDR Write and Training章节分享。

DQ Training

DQ Bus Training也是包括了Voltage Training + Delay Training,其中包括了Read和Write不同场景下的Training。

这里主要基于JESD209-4B分析DQ Bus Training。

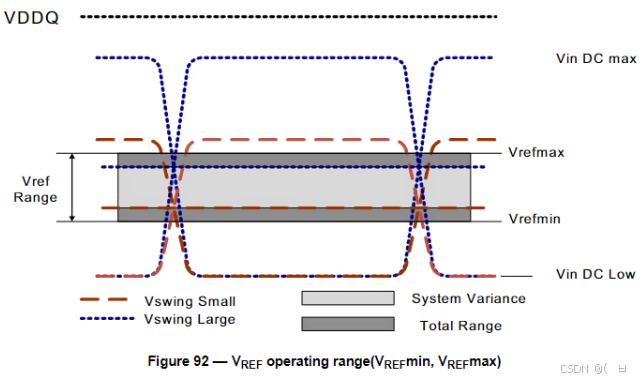

从上图可以看到输入电压范围需要做到不受系统差异(System Variance)影响,满足不同Voltage的Slew Rate(Vswing Small/Large)下的高低电平采样。

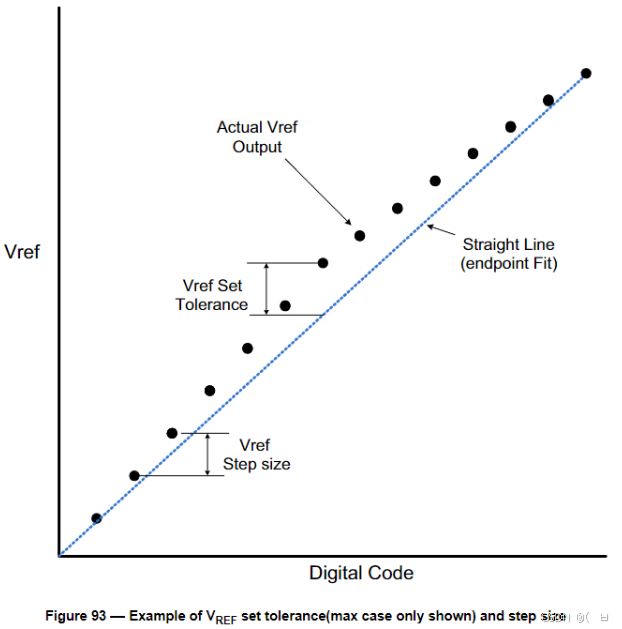

DQ Vref变量包括电压工作范围 - Range,步长 - Step Size,设置误差 - Tolerance,步长时间 - Step Time和有效电平 - Valid Level。

- 步长 - 每一次配置Vref增加或者减少的最小电压粒度。

- 误差 - Vref电压实际值与设定值的偏差。

步长和设置误差的示例图如下:

可以看到还是需要通过Training满足每一步的调整误差不会过大,让Vref-Min到Vref-Max之间的调整误差都在系统可以接受的范围内。

在MC侧,就是通过DQ Bus写一组数据Pattern(Ex:0xAA55 - 10101010 01010101),再从DRAM读回来,根据Fail结果不断调整每个Pin的Vref数值。

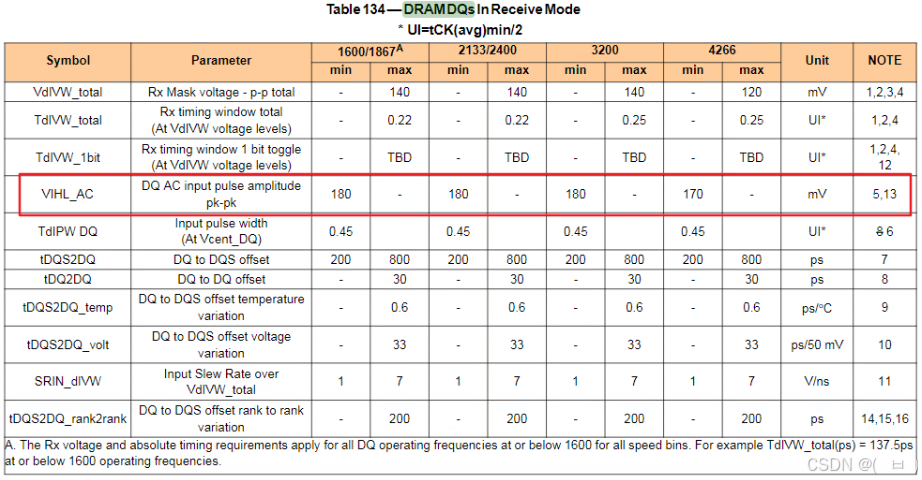

在JEDEC中也有DQ Vref相关的Limitation:

这里DQ相关的Symbol与CA Bus Training里的内容相似,详细内容和SIPI实际波形会在之后的LPDDR Read/Write and Training章节分析。

_今日的最新消息_长沙官网seo收费标准)